Communication

# Oxide Thin-Film Transistor-Based Vertically Stacked Complementary Inverter for Logic and Photo-Sensor Operations

Hyo-Jun Joo $^1$ , Min-Gyu Shin $^1$ , Hwan-Seok Jung $^1$ , Hyun-Seok Cha $^1$ , Donguk Nam $^2$  and Hyuck-In Kwon $^{1,*}$

- School of Electrical and Electronics Engineering, Chung-Ang University, Seoul 06974, Korea; hyojunjun@naver.com (H.-J.J.); 18alsrb@naver.com (M.-G.S.); hwanseok518@cau.ac.kr (H.-S.J.); ckgustjr0803@naver.com (H.-S.C.)

- School of Electrical and Electronic Engineering, Nanyang Technological University, 50 Nanyang Avenue, Singapore 639798, Singapore; dnam@ntu.edu.sg

- Correspondence: hyuckin@cau.ac.kr

Received: 29 October 2019; Accepted: 18 November 2019; Published: 20 November 2019

Abstract: Numerous studies have addressed the utilization of oxide thin-film transistor (TFT)-based complementary logic circuits that are based on two-dimensional (2D) planar structures. However, there are fundamental limits to the 2D planar structured complementary logic circuits, such as a large dimension and a large parasitic resistance. This work demonstrated a vertically stacked three-dimensional complementary inverter composed of a p-channel tin monoxide (SnO) TFT and an n-channel indium-gallium-zinc oxide (IGZO) TFT. A bottom-gate p-channel SnO TFT was formed on the top-gate n-channel IGZO TFT with a shared common gate electrode. The fabricated vertically stacked complementary inverter exhibited full swing characteristics with a voltage gain of ~33.6, a high noise margin of 3.13 V, and a low noise margin of 3.16 V at a supplied voltage of 10 V. The achieved voltage gain of the fabricated complementary inverter was higher than that of the vertically stacked complementary inverters composed of other oxide TFTs in previous works. In addition, we showed that the vertically stacked complementary inverter exhibited excellent visible-light photoresponse. This indicates that the oxide TFT-based vertically stacked complementary inverter can be used as a sensitive photo-sensor operating in the visible spectral range with the voltage read-out scheme.

Keywords: oxide TFT; vertically stacked complementary logic inverter; SnO; IGZO; photo-sensor

## 1. Introduction

Oxide-semiconductor-based thin-film transistors (TFTs) are promising devices for the implementation of electronic circuits in large areas owing to their attractive properties such as high carrier mobility, high uniformity, and low-temperature process compatibility [1–5]. So far, various studies have demonstrated complementary logic circuits using oxide TFTs because they have several advantages in comparison to n-type logic circuits, such as low power consumption, high voltage gain, and good noise immunity [6–15]. While most oxide TFT-based complementary logic circuits reported thus far were based on two-dimensional (2D) planar structures, there exist fundamental limits to the 2D planar structured complementary logic circuits, such as a large dimension due to the horizontally distributed n- and p-channel transistors and a large parasitic resistance caused by long interconnection lengths. The three-dimensional (3D) stacked structure requires more difficult processing techniques in comparison to the 2D planar structure including thermal budget optimization. However, the 3D stacked structure has recently attracted much attention since it can significantly increase the packing density and also improve the drivability of microelectronic circuits by reducing the interconnection

lengths and parasitic resistances [16,17]. In addition, Lin et al. [18] showed that the obtained parasitic capacitance of the 3D stacked silicon complementary inverter was also lower than that of the 2D planar structure. The experimental realization of 3D stacked structure remains challenging, and therefore, only a few research groups have reported vertically stacked complementary inverters composed of oxide TFTs or oxide/organic TFTs [14–17,19,20]. Particularly, to the best of our knowledge, there exists no experimental demonstration of the 3D stacked complementary inverter using indium-gallium-zinc oxide (IGZO) TFT and tin monoxide (SnO) TFT, that are the most representative n-channel and p-channel oxide TFTs.

In this work, we demonstrated a 3D stacked complementary inverter composed of an n-channel IGZO and a p-channel SnO TFT for the first time. The fabricated 3D stacked complementary inverter exhibited full swing characteristics with a high voltage gain of  $\sim$ 33.6 at a supplied voltage ( $V_{\rm DD}$ ) of 10 V. In addition, we investigated the photoresponse of the 3D stacked complementary inverter in the visible region. The obtained results show that the fabricated inverter can be used as a sensitive visible light sensor using the voltage read-out scheme.

### 2. Experimental Procedure

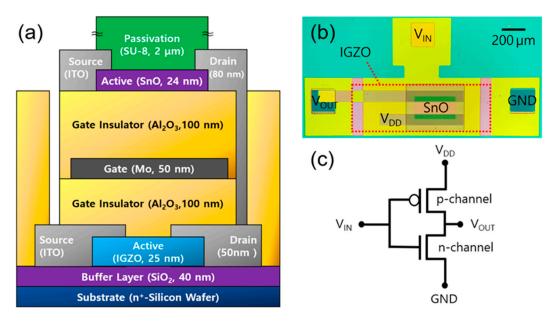

Figure 1a shows the schematic cross-sectional view of the fabricated vertically stacked complementary logic inverter. A 25-nm-thick IGZO channel layer was deposited by RF magnetron sputtering without intentional substrate heating using a 4-inch IGZO target (In:Ga:Zn:O = 1:1:1:4 mol%, purity: 99.99 %) on a heavily doped n-type Si wafer covered by a 40-nm-thick thermal SiO<sub>2</sub> and patterned by a lift-off process. During the deposition of the IGZO channel layer, the working pressure, Ar flow rate, and sputtering power were 5.0 mTorr, 20 sccm, and 50 W, respectively. A 50 nm-thick ITO layer was deposited by DC sputtering as the source/drain electrodes and was patterned using a lift-off process. Then, the deposited thin films were subjected to simultaneous ultraviolet and thermal (SUT) treatments at 150 °C for 1 h in air using a hot plate and ultraviolet light. Ultraviolet light irradiation was performed using a mercury-sourced ultraviolet light with wavelengths of 185 nm (at 10%) and 254 nm (at 90%) during the SUT treatment. The photon flux density of the ultraviolet light was fixed at 15 mW/cm<sup>2</sup>. The SUT treatments were reported to be effective in the densification and condensation of various sputter and solution-processed metal oxide thin films and improve the electrical characteristics and stabilities of IGZO TFTs [21–24]. A 100-nm-thick Al<sub>2</sub>O<sub>3</sub> film was deposited at 200 °C to serve as the gate insulator of the IGZO TFT by atomic layer deposition (ALD) using Al(CH<sub>3</sub>)<sub>3</sub> (trimethylaluminum (TMA)) and  $H_2O$  as precursors. The  $Al_2O_3$  was patterned using photolithography and wet etching to expose the source/drain contact holes. A sputtered molybdenum film with a thickness of 50 nm was used as the common gate electrode and patterned by a lift-off process.

Another 100 nm-thick  $Al_2O_3$  film was deposited at 200 °C by ALD on top of the IGZO TFT to serve as the gate insulator for the SnO TFT. The gate insulator for the SnO TFT was patterned using photolithography and wet etching to expose the common gate and source/drain contact holes of the IGZO TFT. Next, a 24 nm-thick SnO layer was deposited using the RF magnetron sputtering method without intentional substrate heating using a 3-inch Sn target and patterned by a lift-off process. Then, it was annealed at 180 °C for 30 min using hot a plate. During the deposition of the SnO channel layer, the working pressure, gas mixing ratio  $(Ar/O_2)$ , and sputtering power were 3.0 mTorr, 90/4 (sccm/sccm), and 50 W, respectively. An 80 nm-thick ITO layer was deposited by DC sputtering as the source/drain electrodes of the SnO TFT and was patterned using a lift-off process. Next, a 2  $\mu$ m-thick SU-8 layer was formed using the spin coating process as a passivation layer following the formation condition described in detail in our previous work [25]. Finally, the sample was post-annealed at 180 °C for 15 min in air. The optical image and circuit diagram of the fabricated vertically stacked complementary inverter are illustrated in Figure 1b,c, respectively. All electrical measurements for the TFTs and circuits were conducted at room temperature in air using an Agilent 4156C precision semiconductor parameter analyzer (Agilent Technologies., Santa Clara, CA, USA).

**Figure 1.** (a) schematic cross-sectional view, (b) optical image, and (c) circuit diagram of the vertically stacked complementary logic inverter composed of p-type tin monoxide (SnO) and n-type indium-gallium-zinc oxide (IGZO) thin-film transistors (TFTs).

#### 3. Results and Discussion

#### 3.1. Thin Film Characterization

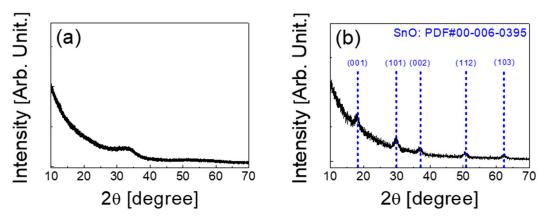

Figure 2a,b display the X-ray diffraction (XRD, Rigaku, Tokyo, Japan) patterns obtained from the IGZO and SnO thin films deposited on the SiO<sub>2</sub>/Si substrate, respectively. The thickness of the thin-films were 25 nm for the IGZO film and 24 nm for the SnO film, respectively. The crystal structures of the IGZO and SnO thin-films were characterized by a D8 Advance X-ray diffractometer from Bruker AXS using  $CuK_{\alpha 1}$  radiation ( $\lambda = 1.54056$  Å). As shown in Figure 2a, the observed broad peak in the range of 30° to 35° is considered as an amorphous halo peak that comes from the IGZO film [26]. Figure 2b presents the crystalline status of the SnO thin-film. SnO possesses a tetragonal PbO-type (P4/nmm) crystallographic structure, in which the spherical Sn 5 s orbitals and O 2p orbitals have almost the same energy levels for effective interaction. Therefore, they can form delocalized and isotropic hybridized orbitals that provide an effective hole transport path [27,28]. Owing to its potential for high hole mobilities, SnO has attracted special attention as a promising p-type oxide semiconductor.

The XRD patterns in Figure 2b are well matched with the (001), (101), (002), (112), and (103) planes of the tetragonal SnO phase (Powder Diffraction File (PDF) card No. 00-006-0395). The average grain size (D) calculated from the SnO (101) peak was 126 Å. The grain size was calculated based on the Debye-Scherrer equation [29]:

$$D = \frac{0.9\lambda}{\beta \cos \theta} \tag{1}$$

where  $\lambda$  is the X-ray wavelength,  $\beta$  is the full width at half maximum of the diffraction peak, and  $\theta$  is the Bragg angle, respectively.

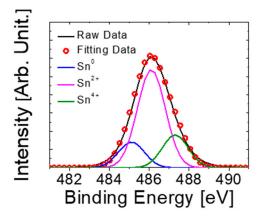

Figure 3 shows the X-ray photoelectron spectroscopy (XPS, Thermo Fisher Scientific, East Grinstead, UK) Sn  $3d_{5/2}$  spectra of the tin oxide thin-film deposited on SiO<sub>2</sub>/Si substrate. The Sn  $3d_{5/2}$  spectra are deconvoluted into three sub-peaks, corresponding to Sn<sup>0</sup>, Sn<sup>2+</sup>, and Sn<sup>4+</sup> components. The binding energy values are fixed at 485.1, 486.0, and 487.3 eV, respectively [30]. The XPS results showed that the deposited thin-film was composed of Sn, SnO, and SnO<sub>2</sub>, but the p-type SnO/Sn<sup>2+</sup> was the dominant phase as observed in Figure 2b.

Materials **2019**, 12, 3815 4 of 10

Figure 2. XRD patterns of the (a) IGZO and (b) SnO thin films used as channel layers in this work.

**Figure 3.** X-ray photoelectron spectroscopy (XPS) Sn  $3d_{5/2}$  spectra of the tin oxide thin-film deposited on the SiO<sub>2</sub>/Si substrate.

#### 3.2. Electrical Characteristics of N-Channel IGZO and P-Channel SnO TFTs

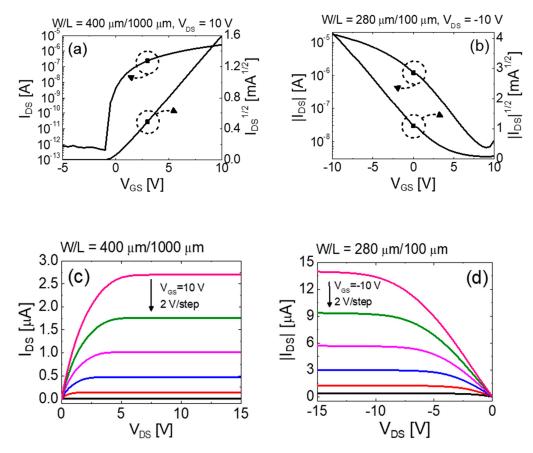

Because it is essential to match the characteristics of n- and p-channel TFTs to obtain excellent complementary logic circuits, individual current-voltage characteristics of vertically stacked top-gate IGZO and bottom-gate SnO TFTs were investigated. The channel width (W) and length (L) of the devices were  $W_n = 400~\mu m$  and  $L_n = 1000~\mu m$  for the n-channel IGZO TFT and  $W_p = 280~\mu m$  and  $L_p = 100~\mu m$  for the p-channel SnO TFT, respectively. The transfer curves (drain current  $I_{DS}$  versus gate-source voltage  $V_{CS}$ ) and output curves ( $I_{DS}$  versus drain-source voltage  $V_{DS}$ ) are shown in Figure 4a,c and Figure 4b,d for n-channel and p-channel TFTs, respectively. The transfer curves were measured at  $V_{DS} = 10~V$  for IGZO TFT and  $V_{DS} = -10~V$  for SnO TFT. The values of saturation mobility ( $\mu_{SAT}$ ), on/off current ratio ( $I_{ON}/I_{OFF}$ ), threshold voltage ( $V_{TH}$ ), and subthreshold swing (SS) were 7.61 cm<sup>2</sup>/V·s, 4.30 × 10<sup>8</sup>, 0.03 V, and 0.29 V/dec for IGZO TFT and 1.34 cm<sup>2</sup>/V·s, 5.75 × 10<sup>3</sup>, 3.15 V, and 3.62 V/dec for SnO TFT, respectively. Here, the values of  $\mu_{SAT}$  were calculated from the following equation:

$$\mu_{\text{SAT}} = \frac{2L}{WC_i} \left( \frac{\partial \sqrt{I_{DS}}}{\partial V_{GS}} \right)^2 \tag{2}$$

where  $C_i$  represents the capacitance of the gate insulator per unit area. The  $\mu_{SAT}$  values of each TFT are comparable with those of previous reports, thereby demonstrating that the stacking process did not deteriorate their performances [31,32]. The values of  $V_{TH}$  were extracted by extrapolating a straight line in  $(I_{DS})^{1/2}$ - $V_{GS}$  plot on the  $V_{GS}$  axis. The SS values which indicate the necessary  $V_{GS}$  to increase  $I_{DS}$  by one decade were calculated from the inverse of the maximum slope of the transfer characteristics. Typical output curves of the IGZO and SnO TFTs are shown in Figure 4c,d, respectively. It is evident that the output curves exhibit clear pinch-off and current saturation.

Materials **2019**, 12, 3815 5 of 10

**Figure 4.** (**a**,**b**) transfer and (**c**,**d**) output curves of the fabricated vertically stacked top-gate IGZO and bottom-gate SnO TFTs, respectively.

## 3.3. Static Performance of Vertically Stacked Complementary Inverter

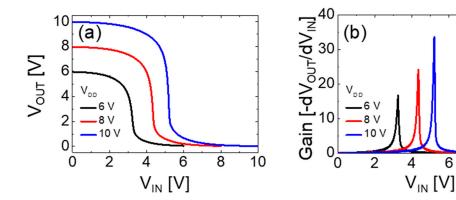

The static performance of the vertically stacked complementary inverter was evaluated using its switching threshold voltage ( $V_{\rm M}$ ), static circuit gain ( $A_{\rm V}=|dV_{\rm OUT}/dV_{\rm IN}|$ ), and noise margin values extracted from the measured inverter voltage transfer characteristics (VTCs). Figure 5a,b show the VTC and static DC gain values of the vertically stacked complementary inverter at different  $V_{\rm DD}$ s of 6, 8, and 10 V, respectively. The values of  $W_{\rm n}/L_{\rm n}$  and  $W_{\rm p}/L_{\rm p}$  of the IGZO and SnO TFTs were 400 µm/1000 µm and 280 µm/100 µm, respectively. The large value of W/L ratio of the SnO TFT compare to that of the IGZO TFT was employed to compensate the difference in  $\mu_{\rm SAT}$  values of IGZO and SnO TFTs and to optimize the inverter performance. Clear inverter action with a full swing is observed in Figure 5a. The performance of the fabricated complementary inverter at different  $V_{\rm DD}$ s is summarized in Table 1.

As shown in Figure 5b, the voltage gain increases with the  $V_{\rm DD}$  and reaches ~33.6 at  $V_{\rm DD}$  = 10 V, which is higher than that of the oxide TFT-based vertically stacked complementary inverters reported in previous works at the same  $V_{\rm DD}$  [14,15]. The relatively high voltage gain may be attributed to the high output resistance of both TFTs, as shown in Figure 4. It is expected that the gain of the inverter can be more increased by improving the mobility and output resistance of TFTs [33]. The noise margin values were extracted from the static VTC shown in Figure 5a. The input-high voltage  $(V_{\rm IH})$  and input-low voltage  $(V_{\rm IL})$  are the input voltage values where the slope of VTC is equal to -1. The output-high voltage  $(V_{\rm OH})$  and output-low voltage  $(V_{\rm OL})$  are the output voltage values for the input-low voltage and input-high voltage, respectively. For  $V_{\rm DD}$  = 10 V, the noise margin high  $(N_{\rm MH}$  =  $V_{\rm OH} - V_{\rm IH})$  and noise margin low  $(N_{\rm ML} = V_{\rm IL} - V_{\rm OL})$  were 3.13 and 3.16 V, respectively. The balanced noise margin may be attributed to the well optimized geometric aspect ratio between the pull-up SnO and pull-down IGZO TFTs.

Materials **2019**, 12, 3815 6 of 10

**Figure 5.** (a) voltage transfer characteristics and (b) static DC gain of the vertically stacked complementary inverter with p-channel SnO TFT ( $W_n/L_n=400~\mu m/1000~\mu m$ ) fabricated on top of the n-channel IGZO TFT ( $W_p/L_p=280~\mu m/100~\mu m$ ) at different  $V_{DD}$ s of 6, 8, and 10 V.

8

10

**Table 1.** Performance of the vertically stacked complementary inverter at different  $V_{\rm DD}$ s.

| $V_{\mathrm{DD}}\left[\mathrm{V}\right]$ | $V_{\mathbf{M}}[\mathbf{V}]$ | $A_{ m V}\left[ m V ight]$ | $N_{ m ML}$ [V] | $N_{ m MH}\left[ m V ight]$ |

|------------------------------------------|------------------------------|----------------------------|-----------------|-----------------------------|

| 6                                        | 3.15                         | 16.7                       | 1.72            | 1.70                        |

| 8                                        | 4.26                         | 24.1                       | 2.55            | 2.30                        |

| 10                                       | 5.18                         | 33.6                       | 3.16            | 3.13                        |

#### 3.4. Visible Light Photoresponse of Vertically Stacked Complementary Inverter for Optoelectronic Applications

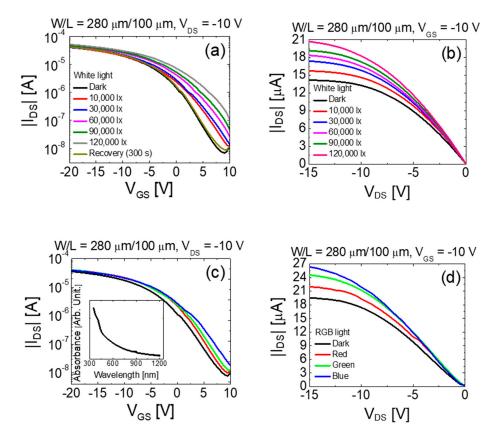

To maximize the potential of vertically stacked complementary inverters beyond the logic applications by including optoelectronic applications such as photo-sensors, we investigated their photoresponse. First, the characteristics of the vertically stacked bottom-gate SnO TFT device upon illumination with visible light was investigated. We performed the electrical measurements in the dark as well as under light illumination at different light intensities and wavelengths. The effects of light illumination on top-gate IGZO TFT was not significant in the turn-on region because the IGZO film is covered by the Mo gate electrode. Figure 6 shows the transfer and output curves of the vertically stacked bottom-gate SnO TFT in the dark and when illuminated on the top of the device with white (wavelength  $\sim 420$ –780 nm), red (wavelength  $\sim 625$ –630 nm), green (wavelength  $\sim 505$ –535 nm), and blue (wavelength  $\sim 460$ –465 nm) light-emitting-diodes (LEDs). The SU-8 for the passivation layer is an optically transparent material for the light with a wavelength of above 400 nm [34], which implies that almost all photons from the LEDs pass through the SU-8 passivation layer without being absorbed.

Figure 6a,b show the transfer and output curves of the SnO TFT obtained under white light illumination with different intensities, respectively. It is evident from Figure 6a that the transfer curve shifts in the positive direction with an increase in SS, and I<sub>OFF</sub> under light illumination. This phenomenon can be attributed to the increase in the conductivity in SnO because the absorbed photon can increase the photogeneration in holes and electrons under light illumination [35]. More photons are expected to be absorbed under more intense light illumination. The transfer curve in Figure 6a shows the recovery behavior in dark condition, following a light illumination of 120,000 lx. The transfer curve recovered to the initial state within 300 s after turning-off a light source. The mechanism which can explain the recovery behavior in Figure 6a is the trapping and detrapping of electrons in bulk defect states of SnO thin-film. The photo generated electrons can be trapped in the bulk states, while holes are able to be more mobile in the semiconductor and they are likely to be swept away. A thermal release of trapped electrons causes the recovery behavior of the transfer curve after turning-off the light. Our previous experiment described the recovery behavior of SnO TFT after terminating the light illumination in detail [36]. The photogenerated carrier effect is also observed in the output characteristics, as shown in Figure 6b. The output resistance decreased with an increase in the intensity of the white light. Figure 6c,d show the transfer and output curves in the dark and

Materials **2019**, 12, 3815 7 of 10

under red-green-blue (RGB) light illumination for a fixed intensity of  $\sim$ 6.5 mW/cm². Figure 6c shows that the transfer curve shifts in the positive direction with an increase in SS and  $I_{\rm OFF}$  under RGB light illumination as compared to the dark condition. The characteristics of the device further changed as the wavelength decreased from the red to the blue light. The output resistance also further decreased with a decrease in the wavelength of the light, as shown in Figure 6d. These results suggest that the changes in the electrical properties of SnO TFT under light illumination strongly depend on the intensity and wavelength (photon energy) of the illuminated light. The inset of the Figure 6c depicts the absorption spectra of the deposited SnO thin-film within the wavelength range of 350–1200 nm. The absorbance increased with a decrease of the wavelength. This result is consistent with the results shown in Figure 6c,d.

**Figure 6.** (a) transfer and (b) output curves of the vertically stacked bottom-gate SnO TFTs under white light illumination with different intensities. (c) transfer and (d) output curves of the SnO TFT under red-green-blue (RGB) light illumination. The RGB light intensity is fixed at ~6.5 mW/cm<sup>2</sup>. The inset of (c) shows the UV-vis absorption spectra of the deposited SnO thin-film.

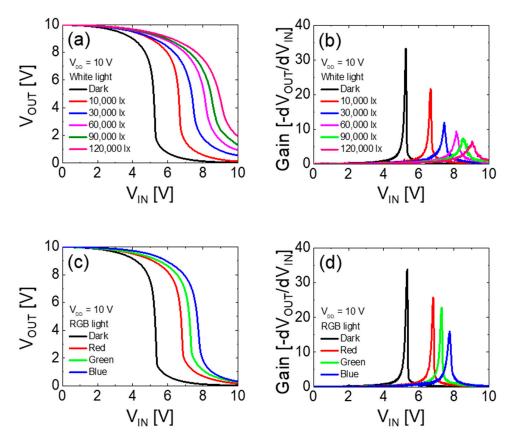

The effects of incident light on the electrical characteristics of the vertically stacked complementary inverter were studied by measuring the photoresponse of the inverter circuit with respect to the illumination intensity and wavelength of the light. The vertically stacked complementary inverter showed excellent photoresponse under visible light illumination. Figure 7a,b show the VTC and static DC gains obtained as a function of the intensities of white light. The  $V_{\rm M}$  was shifted from 5.19 to 8.92 V and the static gain of the inverter was decreased from ~33.2 to ~6.5 with an increase in the light intensity from 0 to 120,000 lx at  $V_{\rm DD}$  = 10 V.

Similar photoresponse was observed under RGB light illumination condition, where the initial VTC curve moved toward a more positive direction as the wavelength of light decreased, as shown in Figure 7c. The  $V_{\rm M}$  was 5.26 V (in dark) and increased under illumination to 6.75 V (red light), 7.22 V (green light), and 7.67 V (blue light) at  $V_{\rm DD} = 10$  V. The values of static voltage gain of the inverter were ~33.5 (in dark), ~25.7 (red light), ~22.8 (green light), and ~16.1 (blue light) at  $V_{\rm DD} = 10$  V, as

shown in Figure 7d. The positive shift in  $V_{\rm M}$  occurred owing to the positive shift in  $V_{\rm TH}$  of the SnO TFT by photogenerated charge carriers under illumination. The decrease in the voltage gain under light illumination can be attributed to the decrease in output resistance of the SnO TFT, as shown in Figure 6 [33,37,38]. The obtained results show the potential for a vertically stacked complementary inverter to be used in sensitive optoelectronic devices that can detect a specific wavelength within the visible light.

**Figure 7.** (a) voltage transfer characteristic (VTC) and (b) static voltage gain curves of the vertically stacked complementary inverter under white light illumination with different intensities. (c) VTC and (d) static voltage gain curves of the inverter under RGB light illumination. The VTCs and corresponding voltage gain curves were measured at  $V_{\rm DD} = 10$  V. The fixed RGB light intensity was ~6.5 mW/cm<sup>2</sup>.

## 4. Conclusions

In summary, we demonstrated a vertically stacked complementary inverter using n-channel IGZO and p-channel SnO TFTs. A bottom-gate p-channel SnO TFT was stacked on top of a top-gate n-channel IGZO TFT using a shared common gate electrode to implement this geometry. The fabricated inverter exhibited clear inverter action with full swing characteristics. The static voltage gain increased with an increase in  $V_{\rm DD}$  and reached ~33.6 when  $V_{\rm DD}$  was equal to 10 V. We also investigated the performance of the vertically stacked complementary inverter under light illumination. The results showed that the fabricated vertically stacked complementary inverter exhibited excellent visible-light photoresponse; this implied that the fabricated complementary inverter can be applied in optoelectronic applications such as photo-sensors and imaging systems.

**Author Contributions:** Conceptualization, H.-J.J. and H.-I.K.; experiment, H.-J.J., M.-G.S., H.-S.J., and H.-S.C.; data analysis, H.-J.J., M.-G.S., and H.-I.K., writing—original draft preparation, H.-J.J.; supervision, D.N. and H.-I.K.; writing—review and editing, H.-I.K.

Materials **2019**, 12, 3815 9 of 10

**Funding:** This work was supported by the National Research Foundation of Korea (NRF) grant funded by the Korea government (MSIP) (No. 2017R1A2A2A14001213) and in part by the Chung-Ang University Graduate Research Scholarship in 2019.

**Conflicts of Interest:** The authors declare no conflict of interest.

#### References

- 1. Nomura, K.; Ohta, H.; Takagi, A.; Kamiya, T.; Hirano, M.; Hosono, H. Room-temperature fabrication of transparent flexible thin-film transistors using amorphous oxide semiconductors. *Nature* **2004**, *432*, 488–492. [CrossRef]

- 2. Fortunato, E.; Barquinha, P.; Martins, R. Oxide semiconductor thin-film transistors: A review of recent advances. *Adv. Mater.* **2012**, 24, 2945–2986. [CrossRef] [PubMed]

- 3. Wang, Z.; Nayak, P.K.; Caraveo-Frescas, J.A.; Alshareef, H.N. Recent developments in p-type oxide semiconductor materials and devices. *Adv. Mater.* **2016**, *28*, 3831–3892. [CrossRef] [PubMed]

- 4. Kamiya, T.; Nomura, K.; Hosono, H. Present status of amorphous In–Ga–Zn–O thin-film transistors. *Sci. Technol. Adv. Mater.* **2010**, *11*, 044305:1–044305:23. [CrossRef]

- 5. Avis, C.; Kim, Y.; Jang, J. Amorphous tin oxide applied to solution processed thin-film transistors. *Materials* **2019**, *12*, 3341. [CrossRef]

- 6. Yang, J.; Wang, Y.; Li, Y.; Yuan, Y.; Hu, Z.; Ma, P.; Zhou, L.; Wang, Q.; Song, A.; Xin, Q. Highly optimized complementary inverters based on p-SnO and n-InGaZnO with high uniformity. *IEEE Electron Device Lett.* **2018**, *39*, 516–519. [CrossRef]

- 7. Li, Y.; Yang, J.; Wang, Y.; Ma, P.; Yuan, Y.; Zhang, J.; Lin, Z.; Zhou, L.; Xin, Q.; Song, A. Complementary integrated circuits based on p-type SnO and n-type IGZO thin-film transistors. *IEEE Electron Device Lett.* **2017**, 39, 208–211. [CrossRef]

- 8. Nayak, P.K.; Caraveo-Frescas, J.A.; Wang, Z.; Hedhili, M.N.; Wang, Q.X.; Alshareef, H.N. Thin film complementary metal oxide semiconductor (CMOS) device using a single-step deposition of the channel layer. *Sci. Rep.* **2014**, *4*, 4672. [CrossRef]

- 9. Wang, Z.; Al-Jawhari, H.A.; Nayak, P.K.; Caraveo-Frescas, J.A.; Wei, N.; Hedhili, M.N.; Alshareef, H.N. Low temperature processed complementary metal oxide semiconductor (CMOS) device by oxidation effect from capping layer. *Sci. Rep.* **2015**, *5*, 9617. [CrossRef]

- 10. Chiu, I.C.; Yun-Shiuan, L.; Min-Sheng, T.; Cheng, I.C. Complementary oxide-semiconductor-based circuits with n-channel ZnO and p-channel SnO thin-film transistors. *IEEE Electron Device Lett.* **2014**, *35*, 1263–1265. [CrossRef]

- 11. Li, Y.-S.; He, J.-C.; Hsu, S.-M.; Lee, C.-C.; Su, D.-Y.; Tsai, F.-Y.; Cheng, I.C. Flexible complementary oxide-semiconductor-based circuits employing n-channel ZnO and p-channel SnO thin-film transistors. *IEEE Electron Device Lett.* **2016**, *37*, 46–49. [CrossRef]

- 12. Zhang, J.; Yang, J.; Li, Y.; Wilson, J.; Ma, X.; Xin, Q.; Song, A. High performance complementary circuits based on p-SnO and n-IGZO thin-film transistors. *Materials* **2017**, *10*, 319. [CrossRef] [PubMed]

- 13. Dhananjay; Chu, C.-W.; Ou, C.-W.; Wu, M.-C.; Ho, Z.-Y.; Ho, K.-C.; Lee, S.-W. Complementary inverter circuits based on p-SnO2 and n-In2O3 thin film transistors. *Appl. Phys. Lett.* **2008**, *92*, 232103. [CrossRef]

- 14. Lee, C.T.; Chen, C.C.; Lee, H.Y. Three dimensional-stacked complementary thin-film transistors using n-type Al: ZnO and p-type NiO thin-film transistors. *Sci. Rep.* **2018**, *8*, 3968. [CrossRef]

- 15. Dindar, A.; Kim, J.B.; Fuentes-Hernandez, C.; Kippelen, B. Metal-oxide complementary inverters with a vertical geometry fabricated on flexible substrates. *Appl. Phys. Lett.* **2011**, *99*, 172104. [CrossRef]

- 16. Baek, C.; Seo, S.M. Vertical organic inverter with stacked pentacene thin film transistors. *Appl. Phys. Lett.* **2009**, 94, 107. [CrossRef]

- 17. Kim, J.B.; Fuentes-Hernandez, C.; Hwang, D.K.; Potscavage, W.J., Jr.; Cheun, H.; Kippelen, B. Vertically stacked hybrid organic–inorganic complementary inverters with low operating voltage on flexible substrates. *Org. Electron.* **2011**, *12*, 45–50. [CrossRef]

- 18. Lin, X.; Zhang, S.; Wu, X.; Chan, M. Local clustering 3-D stacked CMOS technology for interconnect loading reduction. *IEEE Trans. Electron Devices* **2006**, *53*, 1405–1410. [CrossRef]

- 19. Nomura, K.; Aoki, T.; Nakamura, K.; Kamiya, T.; Nakanishi, T.; Hasegawa, T.; Kimura, M.; Kawase, T.; Hirano, M.; Hosono, H. Three-dimensionally stacked flexible integrated circuit: Amorphous

- oxide/polymer hybrid complementary inverter using n-type a-In–Ga–Zn–O and p-type poly-(9, 9-dioctylfluorene-co-bithiophene) thin-film transistors. *Appl. Phys. Lett.* **2010**, *96*, 263509. [CrossRef]

- 20. Kim, J.B.; Fuentes-Hernandez, C.; Hwang, D.K.; Tiwari, S.P.; Potscavage, W.J., Jr.; Kippelen, B. Vertically stacked complementary inverters with solution-processed organic semiconductors. *Org. Electron.* **2011**, 12, 1132–1136. [CrossRef]

- 21. Goutaland, F.; Marin, E.; Michalon, J.Y.; Boukenter, A. Growth of silver nanoparticles of variable and controlled diameter in silica-based and soda-lime glasses by simultaneous continuous ultraviolet irradiation and heat treatment. *Appl. Phys. Lett.* **2009**, *94*, 181108. [CrossRef]

- 22. Tak, Y.J.; Du Ahn, B.; Park, S.P.; Kim, S.J.; Song, A.R.; Chung, K.B.; Kim, H.J. Activation of sputter-processed indium–gallium–zinc oxide films by simultaneous ultraviolet and thermal treatments. *Sci. Rep.* **2016**, *6*, 21869. [CrossRef] [PubMed]

- 23. Tak, Y.J.; Yoon, D.H.; Yoon, S.; Choi, U.H.; Sabri, M.M.; Ahn, B.D.; Kim, H.J. Enhanced electrical characteristics and stability via simultaneous ultraviolet and thermal treatment of passivated amorphous In–Ga–Zn–O thin-film transistors. *ACS Appl. Mater. Interfaces* **2014**, *6*, 6399–6405. [CrossRef]

- 24. Su, B.Y.; Chu, S.Y.; Juang, Y.D.; Chen, H.C. High-performance low-temperature solution-processed InGaZnO thin-film transistors via ultraviolet-ozone photo-annealing. *Appl. Phys. Lett.* **2013**, *102*, 192101. [CrossRef]

- 25. Han, Y.J.; Choi, Y.J.; Cho, I.T.; Jin, S.H.; Lee, J.H.; Kwon, H.I. Improvement of long-term durability and bias stress stability in p-type SnO thin-film transistors using a SU-8 passivation layer. *IEEE Electron Device Lett.* **2014**, *35*, 1260–1262. [CrossRef]

- 26. Li, Y.; Liu, Z.; Jiang, K.; Hu, X. H2 annealing effect on the structural and electrical properties of amorphous InGaZnO films for thin film transistors. *J. Non-Cryst. Solids* **2013**, *378*, 50–54. [CrossRef]

- 27. Ogo, Y.; Hiramatsu, H.; Nomura, K.; Yanagi, H.; Kamiya, T.; Hirano, M.; Hosono, H. p-channel thin-film transistor using p-type oxide semiconductor, SnO. *Appl. Phys. Lett.* **2008**, *93*, 032113. [CrossRef]

- 28. Fortunato, E.; Barros, R.; Barquinha, P.; Figueiredo, V.; Park, S.H.K.; Hwang, C.S.; Martins, R. Transparent p-type SnO x thin film transistors produced by reactive rf magnetron sputtering followed by low temperature annealing. *Appl. Phys. Lett.* **2010**, *97*, 052105. [CrossRef]

- 29. Patterson, A.L. The Scherrer formula for X-ray particle size determination. *Phys. Rev.* 1939, 56, 978. [CrossRef]

- 30. Szuber, J.; Czempik, G.; Larciprete, R.; Koziej, D.; Adamowicz, B. XPS study of the L-CVD deposited SnO2 thin films exposed to oxygen and hydrogen. *Thin Solid Films* **2001**, *391*, 198–203. [CrossRef]

- 31. Ok, K.C.; Oh, S.; Jeong, H.J.; Bae, J.U.; Park, J.S. Effect of alumina buffers on the stability of top-gate amorphous InGaZnO thin-film transistors on flexible substrates. *IEEE Electron Device Lett.* **2015**, *36*, 917–919. [CrossRef]

- 32. Luo, H.; Liang, L.Y.; Liu, Q.; Cao, H.T. Magnetron-sputtered SnO thin films for p-type and ambipolar TFT applications. *ECS J. Solid State Sci. Technol.* **2014**, *3*, Q3091–Q3094. [CrossRef]

- 33. Sedra, A.S.; Smith, K.C. Microelectronic Circuits; Oxford University Press: New York, NY, USA, 1998.

- 34. Parida, O.P.; Bhat, N. Characterization of optical properties of SU-8 and fabrication of optical components. In Proceedings of the International Conference on Optics and Photonics, Chandigarh, India, 30 October–1 November 2009.

- 35. Kimura, M.; Kamada, Y.; Fujita, S.; Hiramatsu, T.; Matsuda, T.; Furuta, M.; Hirao, T. Mechanism analysis of photoleakage current in ZnO thin-film transistors using device simulation. *Appl. Phys. Lett.* **2010**, *97*, 163503. [CrossRef]

- 36. Lee, J.H.; Choi, Y.J.; Jeong, C.Y.; Jung, D.K.; Ham, S.; Kwon, H.I. Electrical instability of p-channel SnO thin-film transistors under light illumination. *IEEE Electron Device Lett.* **2016**, 37, 295–298. [CrossRef]

- 37. Oh, M.S.; Choi, W.; Lee, K.; Hwang, D.K.; Im, S. Flexible high gain complementary inverter using n-Zn O and p-pentacene channels on polyethersulfone substrate. *Appl. Phys. Lett.* **2008**, *93*, 033510-1–033510-3. [CrossRef]

- 38. Fujisaki, Y.; Nakajima, Y.; Kumaki, D.; Yamamoto, T.; Tokito, S.; Kono, T.; Nishida, J.; Yamashita, Y. Air-stable n-type organic thin-film transistor array and high gain complementary inverter on flexible substrate. *Appl. Phys. Lett.* **2010**, *97*, 209, 133303-1–133303-3. [CrossRef]

© 2019 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).