Article

# I–V Characteristics and Electrical Reliability of Metal–Si<sub>x</sub>N<sub>y</sub>–Metal Capacitors as a Function of Nitrogen Bonding Composition

Tae-Min Choi, Eun-Su Jung D, Jin-Uk Yoo D, Hwa-Rim Lee D, Songhun Yoon D and Sung-Gyu Pyo \*D

School of Integrative Engineering, Chung-Ang University, 84, Heukseok-ro, Dongjak-gu, Seoul 06974, Republic of Korea; c79411@gmail.com (T.-M.C.); eunsuj@cau.ac.kr (E.-S.J.); wlsdnr5771@naver.com (J.-U.Y.); ghkfla0725@naver.com (H.-R.L.); yoonshun@cau.ac.kr (S.Y.) \* Correspondence: sgpyo@cau.ac.kr

**Abstract:** In this study, we analyzed the electrical characteristics of metal–insulator–metal (MIM) capacitors fabricated with reference to insulator ( $Si_xN_y$ ) thickness and deposition condition.  $Si_xN_y$  thicknesses of 650 Å, 500 Å, and 400 Å were used with four different conditions designated as MIM (N content 1.49), NEWMIM (N content 28.1), DAMANIT (N content 1.43), and NIT (N content 0.30), deposited by controlling gas flow and RF power as a function of N content. Capacitor characteristics were evaluated mainly in terms of the relationship between leakage current and breakdown voltage (BV). Current–voltage (I–V) characterizations revealed that a higher N–H/Si–H ratio effectively suppressed trapassisted leakage conduction and enhanced dielectric robustness under high-field stress. Among the tested conditions, the NEWMIM process demonstrated the most favorable electrical performance with highest N contents. The MIM and NEWMIM conditions proved most effective among the evaluated processes, achieving sufficient BV values (>20 V) for reliable MIM capacitor operation and proposing a process optimization framework for integrating medium-density  $Si_xN_y$ –based MIM capacitors (2 fF/ $\mu$ m<sup>2</sup>) with sufficiently high BV values in the future.

**Keywords:** MIM; capacitors; metal–insulator–metal; electrical performance;  $Si_xN_y$ ; leakage current density

Academic Editors: Hugo Aguas and Alexandra Ioshi-Imre

Received: 9 April 2025 Revised: 19 May 2025 Accepted: 21 May 2025 Published: 24 May 2025

Citation: Choi, T.-M.; Jung, E.-S.; Yoo, J.-U.; Lee, H.-R.; Yoon, S.; Pyo, S.-G. I–V Characteristics and Electrical Reliability of Metal–Si<sub>x</sub>N<sub>y</sub>–Metal Capacitors as a Function of Nitrogen Bonding Composition. *Micromachines* **2025**, *16*, 615. https://doi.org/ 10.3390/mi16060615

Copyright: © 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

# 1. Introduction

Metal–insulator–metal (MIM) capacitors have garnered significant interest in radio frequency (RF) and analog mixed-signal integrated circuit (IC) applications owing to their low electrode resistance, low parasitic capacitance, high charge mobility, and excellent energy storage capabilities [1–7]. They have been widely utilized as compact energy storage elements in various configurations, including analog ICs, RF circuits, high-power microprocessor units (MPUs), and DRAM applications [8–12]. As RF devices operate at increasingly higher frequencies, achieving a high capacitance per unit area becomes critical for minimizing chip area and enhancing circuit performance [13–15].

To meet these demands, careful optimization of design parameters including electrode materials, insulator selection, dielectric thickness, and deposition methods is essential [16,17]. Among these factors, the dielectric material plays a pivotal role, directly impacting capacitance density (CD), leakage current density (LCD), and device reliability [18–21]. In particular, precise evaluation of current–voltage (I–V) characteristics

is indispensable for understanding intrinsic dielectric behavior and ensuring long-term reliability under practical bias conditions. The capacitance density is theoretically determined by the dielectric constant k and insulator thickness d as expressed by Equation (1) [1,22]:

$$C = \frac{k\varepsilon_0 A}{d} \to \frac{C}{A} = \frac{k\varepsilon_0}{d} \tag{1}$$

where C is the capacitance (F);  $\varepsilon_0$  is the permittivity of vacuum (8.854  $\times$  10<sup>-12</sup>/m); and A is the electrode area. Although decreasing the insulator thickness can effectively increase CD, previous studies have reported that the relative permittivity (k) tends to decrease as thickness is reduced, especially in high-k materials [16,23–25]. Therefore, achieving high capacitance density while maintaining dielectric strength at a reduced thickness remains a significant challenge.

The use of high-k materials can partially mitigate this issue [24,26,27]; however, their implementation demands significant investment in fabrication facilities. In contrast, optimizing the deposition conditions of medium-k materials such as  $\mathrm{Si}_x\mathrm{N}_y$  (k  $\approx$  7) provides a cost-effective and CMOS–compatible strategy to enhance capacitance without extensive process changes [28,29].

In our previous study, we focused on evaluating the capacitance–voltage (C–V) characteristics of  $Si_xN_y$ –based MIM capacitors, particularly examining the impact of silane surface treatment and dielectric thickness variation on capacitance uniformity and voltage/temperature coefficient behaviors [30]. While that work provided insights into dielectric uniformity and capacitance stability, systematic evaluation of leakage current behavior and dielectric breakdown mechanisms as a function of deposition conditions remained unexplored.

Building upon our previous findings, the present study extends the investigation to the I–V characteristics of  $\mathrm{Si}_x\mathrm{N}_y$  films, with a particular focus on optimizing leakage current suppression and breakdown voltage enhancement through deposition condition control.

We aim to establish a process optimization framework for medium-k  $Si_xN_y$ -based MIM capacitors by systematically analyzing the relationship between deposition conditions and electrical reliability. We fabricated MIM capacitors with varying  $Si_xN_y$  thicknesses and deposition conditions. Detailed I–V measurements were conducted to establish correlations between deposition parameters, N content (N–H/Si–H), and leakage current behavior, providing a feasible approach for developing high-reliability, medium-k MIM capacitors suitable for next-generation RF and analog IC applications.

#### 2. Materials and Methods

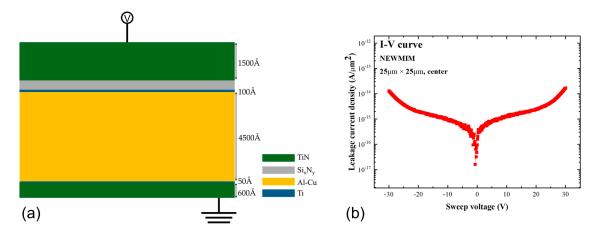

The bottom electrode of the MIM capacitor was prepared using Ti (100 Å)/Al–Cu (4500 Å)/Ti (50 Å)/TiN (600 Å) wiring, and the top electrode was prepared using TiN (1500 Å). The insulator was  $Si_xN_y$ . The capacitor fabrication process was as follows: bottom electrode deposition  $\rightarrow$  bottom electrode scrub  $\rightarrow$  insulator deposition  $\rightarrow$  top metal deposition  $\rightarrow$  MIM PH  $\rightarrow$  MIM  $\rightarrow$  TOP METAL etching  $\rightarrow$  ((CH<sub>3</sub>)<sub>4</sub>NOH:H<sub>2</sub>O, Sigma Aldrich, Incheon, Republic of Korea) cleaning 1  $\rightarrow$  MIM asher  $\rightarrow$  ((CH<sub>3</sub>)<sub>4</sub>NOH:H<sub>2</sub>O) cleaning 2  $\rightarrow$  insulator etching  $\rightarrow$  ACT 935 (wet PR strip solution including amine, Merck, Seoul, Republic of Korea)  $\rightarrow$  UVAS. MIM ET was performed using the endpoint detection method. The fabricated MIM capacitor structure is shown in Figure 1a. The  $Si_xN_y$  insulator was deposited using plasma-enhanced chemical vapor deposition (PECVD), with each condition achieved by precisely adjusting the gas flow ratios (SiH<sub>4</sub>, NH<sub>3</sub>, and N<sub>2</sub>) and RF power. To investigate the effect of nitrogen incorporation on electrical performance, we designed four deposition conditions (MIM, NEWMIM, DAMANIT, and NIT) based on the measured N contents, which were expressed as the N–H/Si–H bonding ratio. The N–H/Si–

H ratios for each condition were 1.49 for MIM, 28.1 for NEWMIM, 1.43 for DAMANIT, and 0.30 for NIT. These values were quantitatively determined using X-ray Photoelectron Spectroscopy (XPS, Thermo Fisher, Waltham, MA, USA) during the process setup stage to evaluate the relative bonding composition in the  $\rm Si_xN_y$  films. Three thicknesses (650 Å, 500 Å, and 400 Å) were applied to evaluate thickness-dependent behavior under each deposition condition.

**Figure 1.** (a) Schematic of fabricated MIM structure and (b) variation in leakage current density with sweep voltage for NEWMIM condition capacitor.

The resulting film properties, including intrinsic stress and deposition uniformity, are summarized in Table 1(a), while the specific process parameters are presented in Table 1(b). To confirm process reliability, Within Wafer and Wafer-to-Wafer uniformity were verified to be within 3%, ensuring reproducibility across all samples.

| <b>Table 1.</b> (a) $Si_xN_y$ film properties and (b) corresponding process condition | <b>Table 1.</b> (a) S | Si <sub>x</sub> N <sub>v</sub> film | properties and ( | b) corres | sponding proce | ess conditions. |

|---------------------------------------------------------------------------------------|-----------------------|-------------------------------------|------------------|-----------|----------------|-----------------|

|---------------------------------------------------------------------------------------|-----------------------|-------------------------------------|------------------|-----------|----------------|-----------------|

| (a)                                 | MIM                   | NEW MIM                | DAMA NIT              | NIT            |

|-------------------------------------|-----------------------|------------------------|-----------------------|----------------|

| Dep. rate                           | ~149 Å/s              | ~29 Å/s                | ~59 Å/s               | 88 Å/s         |

| Within Wafer uniformity $(1\sigma)$ | 1.14%                 | 1.90%                  | 2.34%                 | 2.77%          |

| Wafer-to-Wafer<br>uniformity (1σ)   | 1.58%                 | 2.21%                  | 1.05%                 | 2.30%          |

| Stress                              | $-2.23 \times 10^{9}$ | $-1.75 \times 10^{10}$ | $-2.34 \times 10^{9}$ |                |

| H content (N–H:<br>Si–H)            | 12.7%: 8.5%           | 22.5%: 0.8%            | 10.5%: 7.3%           | 4.4%: 14.8%    |

| N content<br>(N–H/Si–H)             | 1.49                  | 28.1                   | 1.43                  | 0.30           |

| (b)                                 | MIM                   | <b>NEW MIM</b>         | DAMA NIT              | NIT            |

| Step end control                    | By time               | By time                | By time               | By time        |

| Maximum step<br>time                | 4.4 s                 | 22.8 s                 | 11.0 s                |                |

| <b>Endpoint selection</b>           | No endpoint           | No endpoint            | No endpoint           | No endpoint    |

| Pressure                            | Servo 4.25 Torr       | Servo 4.25 Torr        | Servo 4.2 Torr        | Servo 4.5 Torr |

| RF power                            | 690 W                 | 690 W                  | 420 W                 | 425 W          |

| Susceptor<br>temperature            | 400 °C                | 400 °C                 | 400 °C                | 400 °C         |

| Susceptor spacing                   | 620 mils              | 620 mils               | 550 mils              | 475 mils       |

| $N_2$                               | 3800 sccm             | 3800 sccm              | 2500 sccm             | 4000 sccm      |

| $NH_3$                              | 130 sccm              | 50 sccm                | 38 sccm               | 60 sccm        |

| SiH <sub>4</sub>                    | 260 sccm              | 100 sccm               | 110 sccm              | 170 sccm       |

The current–voltage (I–V) characteristics of the fabricated capacitors were measured using an HP4156 semiconductor parameter analyzer (Agilent, Santa Clara, CA, USA) in manual mode, with consideration given to the instrument's resolution. The measurement conditions are summarized in Table 2.

**Table 2.** Measurement conditions for current–voltage characterization.

| Parameter                         | Setting                                                                                                                                                                                             |  |  |

|-----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Sweep voltage                     | -70 V to 70 V                                                                                                                                                                                       |  |  |

| Compliance                        | 10 mA                                                                                                                                                                                               |  |  |

| Forcing                           | Top electrode                                                                                                                                                                                       |  |  |

| Capacitor sizes                   | $10 \times 10 \ \mu\text{m}^2$ , $15 \times 15 \ \mu\text{m}^2$ , $20 \times 20 \ \mu\text{m}^2$ , $25 \times 25 \ \mu\text{m}^2$ , $30 \times 30 \ \mu\text{m}^2$ , $50 \times 50 \ \mu\text{m}^2$ |  |  |

| Measurement points<br>Temperature | Three points (top, center, bottom)  Room temperature                                                                                                                                                |  |  |

### 3. Results and Discussion

The electrical characteristics of the MIM capacitors were determined based on I–V measurements. A total of 12 conditions, involving four  $Si_xN_y$  deposition conditions and three insulator thicknesses, were employed as shown in Table 3. The capacitor size was fixed to  $25 \times 25 \ \mu m^2$  to ensure consistency and eliminate the influence of areal scaling on leakage current levels, and the measurements were recorded at the top, center, and bottom of the wafer under each condition. Figure 1b shows the I–V curve of the MIM capacitor with the 650 Å insulator prepared using the NEWMIM condition. The leakage behavior was symmetrical at 0 V, and this was observed for all the capacitors, regardless of the  $Si_xN_y$  thickness or condition. Table 3 summarizes the LCD values for each  $Si_xN_y$  thickness and condition. The voltage was measured to be 3.7 V with a 10% margin, targeting the typical operating voltage of 3.3 V for MIM capacitors.

**Table 3.** Leakage current densities of MIM capacitors fabricated with different conditions and  $Si_xN_y$  thicknesses.

| Si <sub>x</sub> N <sub>y</sub> Deposition Condition | Thickness (Å) | Leakage Current Density<br>(fA/µm² @ 3.7 V) |

|-----------------------------------------------------|---------------|---------------------------------------------|

|                                                     | 650           | 0.336                                       |

| MIM                                                 | 500           | 0.72                                        |

|                                                     | 400           | 0.32                                        |

|                                                     | 650           | 0.656                                       |

| NEWMIM                                              | 500           | 0.336                                       |

|                                                     | 400           | 0.72                                        |

|                                                     | 650           | 0.416                                       |

| DAMANIT                                             | 500           | 0.432                                       |

|                                                     | 400           | 0.496                                       |

|                                                     | 650           | 0.896                                       |

| NIT                                                 | 500           | 1.728                                       |

|                                                     | 400           | 8.288                                       |

When fabricated using the MIM, NEWMIM, and DAMANIT conditions, the capacitors exhibited LCD values of less than 1 fA/ $\mu$ m² (@3.7 V) for all insulator thicknesses. For the NIT condition, the capacitor with the 650 Å insulator thickness achieved an LCD of less than 1 fA/ $\mu$ m² (@3.7 V), while those with the 500 Å and 400 Å insulator thicknesses exhibited LCD values greater than 1 fA/ $\mu$ m² (@3.7 V).

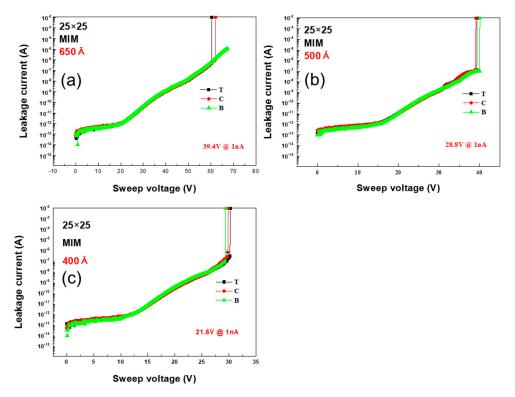

To characterize the BV, voltage sweeps up to 70 V were conducted for each  $Si_xN_y$  thickness and condition, and the BV was the voltage at which the leakage current reached 1 nA. Figure 2 shows the BV measurement results at the top, center, and bottom of the wafer for the capacitor fabricated using the MIM condition. Figure 2a–c present the results for the wafer thicknesses of 650 Å, 500 Å, and 400 Å, respectively; the BV values were 39.4 V, 28.8 V, and 21.6 V for each thickness with the center as the reference. Figure 2 shows that for every thickness, the leakage current behavior was the same at the top, center, and bottom of the wafer and that the BV decreased with thickness.

**Figure 2.** Variation in leakage current with sweep voltage for MIM condition capacitors with  $Si_xN_y$  layer thicknesses of (a) 650 Å, (b) 500 Å, and (c) 400 Å; the corresponding BV values are 39.4 V, 28.8 V, and 21.6 V, respectively.

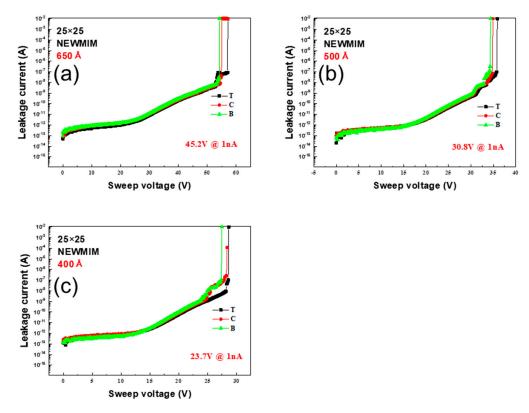

The BV measurements for the NEWMIM condition are shown in Figure 3. Specifically, Figure 3a–c present the results for the wafer thicknesses of 650 Å, 500 Å, and 400 Å, respectively; the BV values were 45.2 V, 30.8 V, and 23.7 V for each thickness with the center as the reference. As with the MIM condition, the leakage current behavior for every thickness was the same at the top, center, and bottom of the wafer, although the BV values were slightly higher.

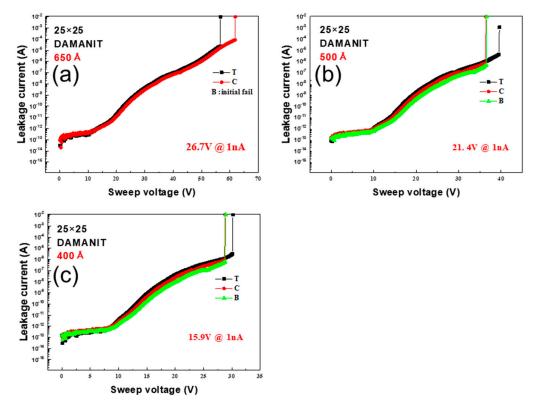

The BV measurements for the DAMANIT condition are shown in Figure 4a–c, which present the results for the wafer thicknesses of 650 Å, 500 Å, and 400 Å, respectively; the BV values were 26.7 V, 21.4 V, and 15.9 V for each thickness with the center as the reference. As with the MIM condition, the leakage current behavior for every thickness was the same at the top, center, and bottom of the wafer; however, the BV values were slightly lower.

**Figure 3.** Variation in leakage current with sweep voltage for NEWMIM condition capacitors with  $Si_xN_y$  layer thicknesses of (a) 650 Å, (b) 500 Å, and (c) 400 Å; the corresponding BV values are 45.2 V, 30.8 V, and 23.7 V, respectively.

**Figure 4.** Variation in leakage current with sweep voltage for DAMANIT condition capacitors with  $Si_xN_y$  layer thicknesses of (a) 650 Å, (b) 500 Å, and (c) 400 Å; the corresponding BV values are 26.7 V, 21.4 V, and 15.9 V, respectively.

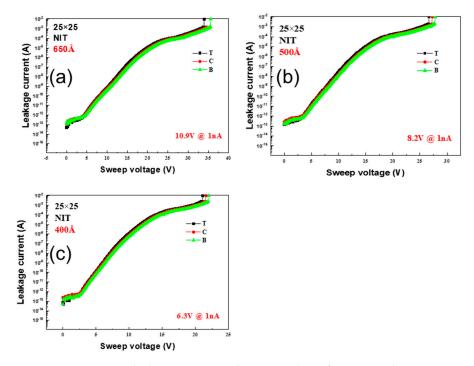

Figure 5 shows the BV measurements for the NIT condition. Specifically, Figure 5a–c depict the results for the wafer thicknesses of 650 Å, 500 Å, and 400 Å, respectively; the BV values were 10.9 V, 8.2 V, and 6.3 V for each thickness with the center as the reference. As with the MIM condition, the leakage current behavior for all the thicknesses was the same at the top, center, and bottom of the wafer; however, the BV values were the lowest among all the conditions.

**Figure 5.** Variation in leakage current with sweep voltage for NIT condition capacitors with  $Si_xN_y$  layer thicknesses of (a) 650 Å, (b) 500 Å, and (c) 400 Å; the corresponding BV values are 10.9 V, 8.2 V, and 6.3 V, respectively.

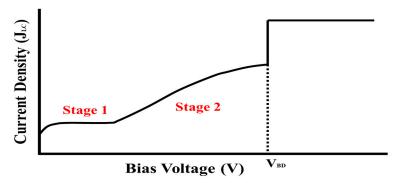

The general I–V characteristics of the MIM capacitor are illustrated in Figure 6. In the initial stage, electrons are injected across the energy barrier between the electrode and dielectric or are captured at trap sites under an applied electric field. Conduction behavior is governed by the Poole–Frenkel mechanism, wherein thermally activated electrons induce a linear relationship between J (Current)/E (Electric Field) and  $\sqrt{E}$  [31,32]. As the bias increases, the available trap sites are progressively saturated, leading to a transition into Stage 2. In this regime, enhanced field emission and detrapping phenomena become dominant [33], resulting in a rapid escalation of current that signifies the onset of dielectric degradation, and when a critical bias is applied, the band bending is amplified, and the tunneling effect, which is minimal in Stages 1 and 2, is maximized, resulting in physical and electrical breakdown [5]. In this study, the breakdown voltage (BV) of the MIM capacitors was operationally defined as the voltage at which the leakage current exceeded 1 nA. Accordingly, the BV corresponds to the bias voltage at which the transition to Stage 2 commences in Figure 6.

The BV values of the MIM capacitors for every  $Si_xN_y$  layer thickness and deposition condition are summarized in Table 4. For all conditions, the BV decreased with thickness. Among the four conditions, the NEWMIM condition provided the best BV value for a given thickness; for the remaining conditions, the BV values decreased in the order of MIM, DAMANIT, and NIT. In MIM capacitors, the leakage current exhibits a strong inverse dependence on dielectric thickness, primarily due to enhancement of the internal electric field as the thickness decreases. A thinner dielectric layer leads to higher field-assisted

emission processes such as Poole–Frenkel conduction, thereby resulting in an exponential increase in leakage current density [31,34].

Figure 6. Schematic representing typical current-voltage behavior of MIM capacitors.

**Table 4.** Breakdown voltages of MIM capacitors fabricated with different  $Si_xN_y$  thicknesses and conditions.

| Si <sub>x</sub> N <sub>y</sub> Deposition Condition | Thickness (Å) | Breakdown Voltages (V) |

|-----------------------------------------------------|---------------|------------------------|

|                                                     | 650           | 39.4                   |

| MIM                                                 | 500           | 28.8                   |

|                                                     | 400           | 21.6                   |

|                                                     | 650           | 45.2                   |

| NEW MIM                                             | 500           | 30.8                   |

|                                                     | 400           | 23.7                   |

|                                                     | 650           | 26.7                   |

| DAMA NIT                                            | 500           | 21.4                   |

|                                                     | 400           | 15.9                   |

|                                                     | 650           | 10.9                   |

| NIT                                                 | 500           | 8.2                    |

|                                                     | 400           | 6.3                    |

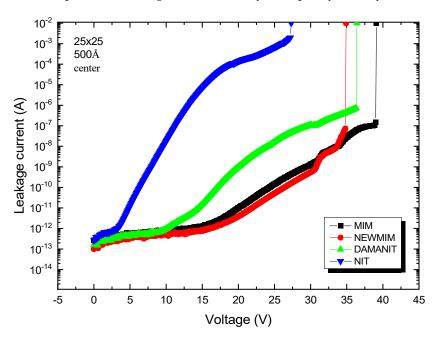

To interpret the BV values based on the condition, the N–H/Si–H ratio for each condition is shown in Table 1. Further, Figure 7 shows the variation in leakage current with the bias for each condition at the same thickness (500 Å). To interpret the BV values based on material conditions, the N–H/Si–H ratio for each condition is summarized in Table 1. Figure 6 presents the variation in leakage current with applied bias for each condition at a fixed thickness of 500 Å. A higher N–H/Si–H ratio correlates with a lower leakage current density (LCD) and higher breakdown voltage (BV). Among the samples, the NEWMIM condition exhibited the highest N–H/Si–H ratio at 28.1, whereas the NIT condition showed the lowest value of 0.30. Correspondingly, as shown in Figure 7, the leakage current in Stage 2 was lowest for NEWMIM and highest for NIT. This trend is attributed to the difference in trap density within the dielectric.

Several studies have reported that for MIM capacitors employing amorphous  $Si_xN_y$  films prepared by plasma-enhanced chemical vapor deposition, an increased N–H/Si–H bonding ratio (i.e., higher N content) leads to a reduction in leakage current [13,35–39]. In  $Si_xN_y$  films, a higher N–H bond concentration effectively reduces the trap density within the dielectric. As a result, trap-assisted tunneling and field-enhanced detrapping are suppressed, leading to a slower increase in leakage current under high electric field stress. Conversely, films with higher trap densities exhibit enhanced trap filling and detrapping, facilitating additional leakage pathways and causing a steeper escalation in leakage current. The replacement of weaker Si–H bonds with stronger Si–N bonds suppresses the formation

of dangling bonds, thus mitigating trap-assisted conduction mechanisms. This is consistent with the Poole–Frenkel framework, where lower trap densities diminish field-enhanced carrier emission, contributing to higher breakdown voltages. Thus, increasing the N–H bonding ratio is an effective strategy to improve the high-field leakage characteristics of  $Si_xN_y$ –based MIM structures. Under this assumption, our experiments showed that  $Si_xN_y$  thin films fabricated under NEWMIN and MIM conditions fulfilled high BV values of more than 20 V even at a thickness of 400 Å. Furthermore, a comparison across different film thicknesses highlights that under high nitrogen incorporation (as in the NEWMIM and MIM conditions), the BV values at 400 Å exceeded those of 500 Å films fabricated under lower nitrogen conditions (DAMANIT and NIT). This observation emphasizes that dielectric performance is governed more by film quality than by thickness alone.

**Figure 7.** Variation in leakage current with sweep voltage for MIM capacitors fabricated using different conditions with a  $Si_xN_y$  layer thickness of 500 Å.

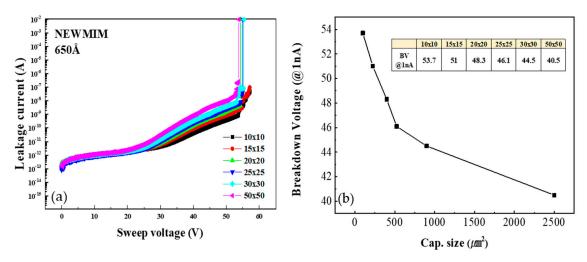

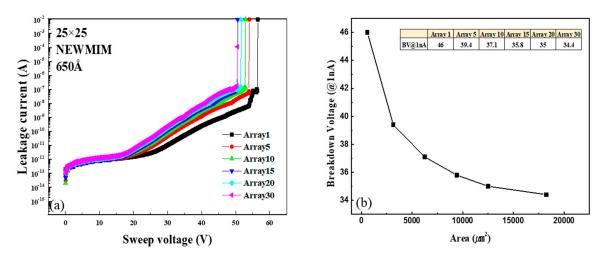

To understand the relationship between the BV characteristics and capacitor size, the BV values were measured for the  $10\times10$ ,  $15\times15$ ,  $20\times20$ ,  $25\times25$ ,  $30\times30$ , and  $50\times50~\mu m^2$  capacitors fabricated using the NEWMIM condition with the 650 Å insulator thickness. Figure 8a shows the I–V curves, while Figure 8b shows the change in the BV with increasing capacitor size. The BV value is observed to decrease by up to 24.5% as the capacitor size increases. Also, to evaluate the dependence of the BV characteristics on the number of capacitor arrays, the BV values were measured for 1, 5, 10, 15, 20, and 30 arrays of the  $25\times25~\mu m^2$  capacitor fabricated using the NEWMIM condition with the 650 Å insulator thickness. Figure 9a shows the I–V curve, and Figure 9b shows the change in the BV value with the number of arrays. As the number of arrays (i.e., as the capacitance area) increases, the BV decreases by up to 24.7%.

The observed decrease in BV with increasing capacitor size and array number can be attributed to area-dependent reliability degradation mechanisms. As the physical area of the capacitor increases, the probability of encountering pre-existing defects within the dielectric also increases, which leads to a higher likelihood of localized dielectric breakdown. These results suggest that for large-area MIM capacitors, careful control of dielectric quality and design considerations to mitigate edge effects are essential to maintain high reliability. Nevertheless, capacitors under the NEWMIM conditions adopted in this study showed stable BV values for all areas and arrays.

**Figure 8.** (a) Variation in leakage current with sweep voltage and (b) variation in breakdown voltage for MIM capacitors of different sizes.

**Figure 9.** (a) Variation in leakage current with sweep voltage and (b) variation in breakdown voltage for MIM capacitors with different total capacitance areas.

## 4. Conclusions

In this study, the electrical (I–V) characteristics of MIM capacitors were evaluated with respect to Si<sub>x</sub>N<sub>v</sub> thickness and deposition condition. To enhance the reliability of the observed electrical trends, especially the correlation between nitrogen content and breakdown behavior, I-V measurements were conducted at three distinct positions—top, center, and bottom—of the wafer for each condition and thickness. As nitrogen incorporation in films increased, breakdown voltage (BV) characteristics are enhanced. Across all insulator thicknesses, capacitors fabricated using the NEWMIM condition (N content 28.1) consistently exhibited higher BV values (@1 nA) than those fabricated under other conditions. Notably, both MIM (N content 1.49) and NEWMIM conditions achieved BV values exceeding 20 V even at a reduced thickness of 400 Å, underscoring the impact of optimized bonding environments on dielectric reliability. These results suggest that higher N contents result in improved dielectric quality through reduced trap site formation, providing a robust basis for high-field reliability in scaled MIM structures. The comprehensive I-V dataset, spanning three film thicknesses and four deposition conditions, supports a process optimization framework grounded in bonding structure control. These findings demonstrate the feasibility of developing medium-density (2 fF/µm<sup>2</sup>) MIM capacitors

with sub-400  $\mbox{\normalfont\AA}$  insulator layers, enabling increased capacitance density without sacrificing breakdown strength.

Beyond the immediate findings, this study suggests that lower-thickness  $\mathrm{Si_xN_y}$  layers can support high-density integration without significant loss of dielectric strength. The MIM and NEWMIM processes also appear compatible with standard CMOS BEOL thermal budgets, offering practical integration potential. Future work should explore barrier layer incorporation, stack engineering, and accelerated reliability testing to validate the long-term stability of these MIM structures.

**Author Contributions:** Conceptualization, T.-M.C., E.-S.J., and S.-G.P.; methodology, S.Y. and S.-G.P.; validation, T.-M.C., E.-S.J., and H.-R.L.; writing—original draft preparation, T.-M.C. and J.-U.Y.; supervision, S.Y. and S.-G.P.; project administration, S.-G.P. All authors have read and agreed to the published version of the manuscript.

**Funding:** This work was supported by the Technology Innovation Program (or Industrial Strategic Technology Development Program-Public-Private joint investment semiconductor R&D program (K-CHIPS) to foster high-quality human resources) ("RS-2023-00237003", high selectivity etching technology using cryoetch) funded by the Ministry of Trade, Industry, and Energy (MOTIE, Korea) (1415187674). This work was also supported by the Technology Innovation Program (No. 20022472) funded by the Ministry of Trade, Industry, and Energy (MOTIE, KOREA).

**Data Availability Statement:** The original contributions presented in the study are included in the article; further inquiries can be directed to the corresponding author.

Conflicts of Interest: The authors declare no conflicts of interest.

#### References

- Xiong, L.; Hu, J.; Yang, Z.; Li, X.; Zhang, H.; Zhang, G. Dielectric Properties Investigation of Metal–Insulator–Metal (MIM) Capacitors. *Molecules* 2022, 27, 3951. [CrossRef] [PubMed]

- 2. Khaldi, O.; Jomni, F.; Gonon, P.; Mannequin, C.; Yangui, B. Investigation of electrical properties of HfO<sub>2</sub> metal–insulator–metal (MIM) devices. *Appl. Phys. A* **2014**, *116*, 1647–1653. [CrossRef]

- 3. Shin, H.; Choi, H.; Lim, J.; Lee, W.; Mohit, K.; Kim, Y.; Jung, H.-S.; Lim, H.; Seo, H. Interfacial engineering of ZrO<sub>2</sub> metal-insulator-metal capacitor using Al<sub>2</sub>O<sub>3</sub>/TiO<sub>2</sub> buffer layer for improved leakage properties. *J. Asian Ceram. Soc.* **2022**, *10*, 649–659. [CrossRef]

- 4. Sul, W.S.; Pyo, S.G. RF Characteristic Analysis Model Extraction on the Stacked Metal–Insulator–Metal Capacitors for Radio Frequency Applications. *IEEE Trans. Electron Devices* **2014**, *61*, 3011–3013. [CrossRef]

- 5. Mu, J.; Chou, X.; Ma, Z.; He, J.; Xiong, J. High-Performance MIM Capacitors for a Secondary Power Supply Application. *Micromachines* **2018**, *9*, 69. [CrossRef]

- 6. Patil, S.R.; Barhate, V.N.; Patil, V.S.; Agrawal, K.S.; Mahajan, A.M. The effect of post-deposition annealing on the chemical, structural and electrical properties of Al/ZrO<sub>2</sub>/La<sub>2</sub>O<sub>3</sub>/ZrO<sub>2</sub>/Al high-k nanolaminated MIM capacitors. *J. Mater. Sci. Mater. Electron.* **2022**, *33*, 11227–11235. [CrossRef]

- 7. Banerjee, P.; Perez, I.; Henn-Lecordier, L.; Lee, S.B.; Rubloff, G.W. Nanotubular metal-insulator-metal capacitor arrays for energy storage. *Nat. Nanotechnol.* **2009**, *4*, 292–296. [CrossRef]

- 8. Lim, H.; Choi, J.H.; Cho, G.; Chang, J.; Kim, Y.; Jung, H.-S.; Shin, K.-S.; Seo, H.; Jeon, H. Study of Metal–Dielectric Interface for Improving Electrical Properties and Reliability of DRAM Capacitor. *Adv. Mater. Technol.* **2023**, *8*, 2200412. [CrossRef]

- 9. Lau, W.S. Some Key Modifications of Theory Required to Understand the Leakage Current Mechanisms for MIM Capacitors used in Dram Technology. In Proceedings of the 2020 China Semiconductor Technology International Conference (CSTIC), Shanghai, China, 26 June–17 July 2020; pp. 1–3.

- 10. Ding, S.-J.; Hu, H.; Lim, H.; Kim, S.; Yu, X.; Zhu, C.; Li, M.; Cho, B.J.; Chan, D.S.; Rustagi, S.C. High-performance MIM capacitor using ALD high-k HfO<sub>2</sub>-Al<sub>2</sub>O<sub>3</sub> laminate dielectrics. *IEEE Electron Device Lett.* **2003**, 24, 730–732. [CrossRef]

- 11. Das, N.; Karar, A.; Vasiliev, M.; Tan, C.L.; Alameh, K.; Lee, Y.T. Analysis of nano-grating-assisted light absorption enhancement in metal–semiconductor–metal photodetectors patterned using focused ion-beam lithography. *Opt. Commun.* **2011**, 284, 1694–1700. [CrossRef]

12. Wu, K.; Zhang, H.; Chen, Y.; Luo, Q.; Xu, K. All-silicon microdisplay using efficient hot-carrier electroluminescence in standard 0.18µm CMOS technology. *IEEE Electron Device Lett.* **2021**, 42, 541–544. [CrossRef]

- 13. van Delden, M.H.W.M.; van der Wel, P.J. Reliability and electric properties for PECVD a-SiN/sub x/:H films with an optical band-gap ranging from 2.5 to 5.38 eV. In Proceedings of the 2003 IEEE International Reliability Physics Symposium Proceedings, 2003. 41st Annual, Dallas, TX, USA, 30 March–4 April 2003; pp. 293–297.

- 14. Chang, C.S. Applications of Metal-Insulator-Metal (MIM) Capacitors; International Sematech: Austin, TX, USA, 2000.

- 15. Choi, E.; Kim, A.; Kwon, S.H.; Pyo, S.G. Effect of Interface Treatment on the Voltage Linearity in 8 fF/μm2 High-k Dielectric and Combination Stacks on Metal Insulator Metal (MIM) Capacitor. *Sci. Adv. Mater.* **2018**, *10*, 467–470. [CrossRef]

- 16. Li, W.; Lu, X.; Yang, R.; Liang, F.; Chen, W.; Xie, Z.; Zheng, J.; Zhu, J.; Huang, Y.; Yue, W.; et al. Highly sensitive and reproducible SERS substrates with binary colloidal crystals (bCCs) based on MIM structures. *Appl. Surf. Sci.* **2022**, *597*, 153654. [CrossRef]

- 17. Jeon, S.; Sung, S.-K.; Jang, E.-H.; Jeong, J.; Surabhi, S.; Choi, J.-H.; Jeong, J.-R. Multilayer metal-oxide-metal nanopatterns via nanoimprint and strip-off for multispectral resonance. *Appl. Surf. Sci.* **2018**, 428, 280–288. [CrossRef]

- 18. Shin, Y.; Nam, S.G.; Heo, J.; Nam, S. Broadband Characterization of Thin Dielectrics Using Heterolayer and Monolayer MIM Capacitors. *IEEE Trans. Instrum. Meas.* **2022**, *71*, 6006008. [CrossRef]

- 19. PS, S.; Jayan, J.S.; Saritha, A.; Suresh Babu, V.; G, S. Synthesis and Performance Evaluation of Ba<sub>x</sub>Sr<sub>1</sub>—xTiO<sub>3</sub> Ceramic-Based MIM Capacitor for Energy Storage Application. *Integr. Ferroelectr.* **2020**, 212, 177–189. [CrossRef]

- Gopika, S.; Shyju, S. Performance Evaluation of Symmetric Supercapacitors based on Pelletized MnO<sub>2</sub> and MnO<sub>2</sub> doped V<sub>2</sub>O<sub>5</sub> Electrodes. In Proceedings of the 2020 4th International Conference on Electronics, Communication and Aerospace Technology (ICECA), Coimbatore, India, 5–7 November 2020; pp. 281–288.

- 21. Jin Chung, J.; Hyuk Kim, T.; Ahsan Saeed, M.; Won Shim, J. Laminated indium-oxide/molybdenum-oxide nanocomposites for high-work-function electrodes in organic photovoltaics and capacitor devices. *Appl. Surf. Sci.* **2023**, *610*, 155526. [CrossRef]

- 22. Guo, Y.; Wang, S.; Du, X.; Liang, S.; Huang, S.; Peng, S.; Xie, Y.; Ma, M.; Xiong, L. Construction of ultrahigh capacity density carbon nanotube based MIM capacitor. *Energy Storage Mater.* **2023**, *63*, 103064. [CrossRef]

- 23. Han, D.H.; Choi, S.J.; Kim, Y.; Jeon, W. Investigating Dielectric Relaxation Currents for a Deeper Understanding of Capacitance and Interface in Metal–Insulator–Metal Capacitor. *IEEE Trans. Dielectr. Electr. Insul.* **2024**, *31*, 1276–1280. [CrossRef]

- 24. Natori, K.; Otani, D.; Sano, N. Thickness dependence of the effective dielectric constant in a thin film capacitor. *Appl. Phys. Lett.* **1998**, 73, 632–634. [CrossRef]

- 25. Miller, J.R. Perspective on electrochemical capacitor energy storage. Appl Surf Sci 2018, 460, 3–7. [CrossRef]

- 26. Nam, M.; Kim, A.; Kang, K.; Choi, E.; Kwon, S.H.; Lee, S.J.; Pyo, S.G. Characterization of atomic layer deposited Al<sub>2</sub>O<sub>3</sub>/HfO<sub>2</sub> and Ta<sub>2</sub>O<sub>5</sub>/Al<sub>2</sub>O<sub>3</sub> combination stacks. *Sci. Adv. Mater.* **2016**, *8*, 1958–1962. [CrossRef]

- 27. Jamison, P.C.; Massey, J.; Ando, T.; Cartier, E.A.; Jagannathan, H.; Chen, P.J.; Liu, E.; Romero, A.; Naczas, S.; Narayanan, V.; et al. BEOL Compatible High-Capacitance MIMCAP Structure Using a Novel High k Material. *ECS Trans.* **2020**, *97*, 81. [CrossRef]

- 28. Holden, K.E.K.; Hall, G.D.R.; Cook, M.; Kendrick, C.; Pabst, K.; Greenwood, B.; Daugherty, R.; Gambino, J.P.; Allman, D.D.J. Dielectric Relaxation, Aging and Recovery in High-K MIM Capacitors. In Proceedings of the 2021 IEEE International Reliability Physics Symposium (IRPS), Monterey, CA, USA, 21–25 March 2021; pp. 1–10.

- 29. Spahr, H.; Nowak, C.; Hirschberg, F.; Reinker, J.; Kowalsky, W.; Hente, D.; Johannes, H.-H. Enhancement of the maximum energy density in atomic layer deposited oxide based thin film capacitors. *Appl. Phys. Lett.* **2013**, *103*, 042907. [CrossRef]

- 30. Choi, T.-M.; Jung, E.-S.; Yoo, J.-U.; Lee, H.-R.; Pyo, S.-G. Capacitance–Voltage Fluctuation of Si<sub>x</sub>N<sub>y</sub>-Based Metal–Insulator–Metal Capacitor Due to Silane Surface Treatment. *Micromachines* **2024**, *15*, 1204. [CrossRef] [PubMed]

- 31. Allers, K.H. Prediction of dielectric reliability from I−V characteristics: Poole–Frenkel conduction mechanism leading to √E model for silicon nitride MIM capacitor. *Microelectron. Reliab.* **2004**, *44*, 411–423. [CrossRef]

- 32. Hung, C.-C.; Oates, A.S.; Lin, H.-C.; Chang, Y.-E.P.; Wang, J.-L.; Huang, C.-C.; Yau, Y.-W. An innovative understanding of metal-insulator-metal (MIM)-capacitor degradation under constant-current stress. *IEEE Trans. Device Mater. Reliab.* 2007, 7, 462–467. [CrossRef]

- 33. Koszewski, A.; Souchon, F.; Ouisse, T. Conduction and trapping in RF MEMS capacitive Switches with a SiN Layer. In Proceedings of the 2009 European Solid State Device Research Conference, Athens, Greece, 14–18 September 2009; pp. 339–342.

- 34. Chiu, F.-C. A Review on Conduction Mechanisms in Dielectric Films. Adv. Mater. Sci. Eng. 2014, 2014, 578168. [CrossRef]

- 35. Zhang, S.; Wei, K.; Xiao, Y.; Ma, X.-H.; Zhang, Y.-C.; Liu, G.-G.; Lei, T.-M.; Zheng, Y.-K.; Huang, S.; Wang, N.; et al. Effect of SiN:Hx passivation layer on the reverse gate leakage current in GaN HEMTs. *Chin. Phys. B* **2018**, 27, 097309. [CrossRef]

- 36. Ho, C.-C.; Chiou, B.-S. Effect of size and plasma treatment and the application of Weibull distribution on the breakdown of PECVD SiNx MIM capacitors. *Microelectron. Eng.* **2008**, *85*, 110–114. [CrossRef]

- 37. Suzuki, M.; Sagawa, M.; Kusunoki, T.; Nishimura, E.; Ikeda, M.; Tsuji, K. Enhancing electron-emission efficiency of MIM tunneling cathodes by reducing insulator trap density. *IEEE Trans. Electron Devices* **2012**, *59*, 2256–2262. [CrossRef]

38. Gupta, H.; Van Overstraeten, R. Role of trap states in the insulator region for MIM characteristics. *J. Appl. Phys.* **1975**, 46, 2675–2682. [CrossRef]

39. Okada, K.; Ito, Y.; Suzuki, S. A new model for dielectric breakdown mechanism of silicon nitride metal-insulator-metal structures. In Proceedings of the 2016 IEEE International Reliability Physics Symposium (IRPS), Pasadena, CA, USA, 17–21 April 2016; pp. 3A-6-1–3A-6-6.

**Disclaimer/Publisher's Note:** The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content.