# Self-Refresh Memory in Pixel Circuit With 18-bit Color Depth for Liquid Crystal Displays

Won-Been Jeong<sup>®</sup>, Jae-Hee Jo<sup>®</sup>, Sang-Hoon Kim<sup>®</sup>, Hoon-Ju Chung<sup>®</sup>, and Seung-Woo Lee<sup>®</sup>, Senior Member, IEEE

Abstract-In this letter, we propose memory in pixel (MIP) circuit that achieves 6-bit depth per sub-pixel, resulting in an 18-bit color depth for RGB displays. The circuit integrates two memory cells, each storing 3-bit gray level data, allowing the pixel to self-refresh without requiring continuous input from the graphics processor. This is achieved with a novel driving scheme that eliminates the need for continuous data processing for a static image. The proposed circuit achieves a 97.2% reduction in power consumption compared to the conventional pixel circuit. Furthermore, it extends the bit depth per sub-pixel from 3-bit in our previous work to 6-bit, significantly enhancing grayscale resolution. In addition, the circuit supports gamma correction, allowing precise grayscale reproduction across the full dynamic range.

Index Terms—Low power display, memory in pixel (MIP), thin film transistor (TFT), self-refresh.

#### I. Introduction

PANEL self-refresh (PSR) is a technology that enables displays to maintain static images without continuous operation of the system's graphics processor [1], [2], [3]. In conventional display systems, the graphics processor renders and delivers every image frame to the panel in a repetitive sequence [1]. However, for static images, this constant updating of image data becomes redundant and consumes unnecessary system resources [2]. PSR addresses this inefficiency by storing images in a frame memory within the panel. This mechanism allows the panel to display static images without requiring additional input from the processor. Consequently, the system can enter an idle mode where the processor neither renders nor delivers image information, resulting in significant power savings [3].

Despite its advantages, PSR implementation faces challenges. The technology requires an additional frame buffer to store image data. As a display resolution increases, the volume of data to be stored grows correspondingly, leading

Received 10 April 2025; revised 24 April 2025; accepted 30 April 2025. Date of publication 5 May 2025; date of current version 1 July 2025. This work was supported in part by the Basic Science Research Program through NRF under Grant NRF-2020R1I1A3A04037918 and in part by the Brain Korea 21 Four Program in 2024. The review of this letter was arranged by Editor T.-Y. Seong. (Corresponding authors: Seung-Woo Lee; Hoon-Ju Chung.)

Won-Been Jeong, Sang-Hoon Kim, and Seung-Woo Lee are with the Department of Information Display, Kyung Hee University, Dongdaemun, 02447, South Korea (e-mail: seungwoolee@khu.ac.kr).

Jae-Hee Jo is with Samsung Display Company Ltd., Yongin-si, Gyeonggi-do 17113, South Korea.

Hoon-Ju Chung is with the School of Electronic Engineering, Kumoh National Institute of Technology, Gumi, Gyeongsangbuk-do 39177, South Korea (e-mail: hjchung@kumoh.ac.kr).

Digital Object Identifier 10.1109/LED.2025.3566707

to increased costs for frame buffers [3]. To address these challenges, extensive research has been conducted on memory in pixel (MIP) circuits for liquid crystal displays (LCDs). These MIP circuits aim to display static images without a frame buffer by integrating memory within the pixel circuit [4], [5], [6], [7], [8], [9], [10], [11]. MIP designs typically incorporate automatic polarity inversion of pixel voltages to prevent image sticking.

MIP circuits have been developed in two primary categories. The static type requires more than six thin-film transistors (TFTs) [4], [5], [6], which can impede the achievement of high-resolution. In contrast, the dynamic type utilizes one capacitor to store pixel voltage and more than one TFT [7], [8], [9]. This design offers advantages for high-resolution displays. A significant limitation of early MIP circuits was their ability to drive only one-bit depth displays [7], [10], [11]. This constraint resulted in inaccurate color representation and artifacts along object edges [12]. Consequently, increasing the bit depth became essential for implementing high-quality

In our previous work, we proposed an MIP circuit for LCD comprising two TFTs and one capacitor, which was verified to implement 3-bit depth [13]. Building on this foundation, this letter introduces a 6-bit depth MIP circuit consisting of four TFTs and two capacitors. We have employed a novel driving scheme and validated the proposed circuit's 6-bit depth capability through experimental measurements.

## II. PROPOSED CIRCUIT

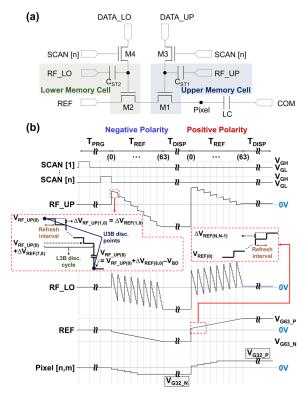

Fig. 1 illustrates the proposed MIP circuit and its corresponding timing diagram. The circuit comprises two memory cells, each capable of discriminating 3-bit depth, thereby enabling a total of six bits for gray level representation. Upper memory cell determines the upper three bits (U3B), while lower memory cell determines the lower three bits (L3B). The combination of U3B and L3B forms a six-bit value corresponding to a gray level, which determines the pixel voltage. U3B and L3B are programmed using data voltages (V<sub>DATA UP</sub>, V<sub>DATA LO</sub>), which can assume eight distinct voltage levels. RF\_UP and RF\_LO are global signals for selfrefresh, modulating the gate voltages of M1 and M2 through capacitive coupling with C<sub>ST1</sub> and C<sub>ST2</sub>, respectively. REF functions as a global signal that charges the pixel node based on the gate-source voltages (V<sub>GS</sub>) of M1 and M2.

## A. Programming Period (T<sub>PRG</sub>)

The voltages of DATA UP and DATA LO are programmed into pixels as eight distinct voltage levels, corresponding to

Fig. 1. (a) Proposed circuit and (b) Timing diagram for the circuit.

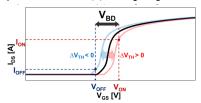

Fig. 2. Minimum  $V_{BD}$  defined by  $V_{ON} - V_{OFF}$ .

the U3B and L3B, respectively. The global signals of RF\_UP, RF\_LO, and REF are kept at 0V indicated by the blue horizontal lines in Fig. 1.

#### B. Refresh Period (T<sub>REF</sub>)

During the refresh period, all pixels are refreshed simultaneously using global signals. The REF signal exhibits negative/positive stepped waveforms consisting of 64 voltage levels corresponding to gray level 0 to 63, as shown in Fig. 1(b). We define  $V_{BD}$  as the key parameter for bit discrimination voltage to be larger than the difference between  $V_{ON}$  and  $V_{OFF}$ , as illustrated in Fig. 2.  $I_{ON}$  represents a high current level sufficient to charge the pixel node to REF voltage within unit refresh interval, while  $I_{OFF}$  is a low current level that results in almost no changes of the pixel voltage. Since  $V_{ON}$  and  $V_{OFF}$  can vary due to the threshold voltage ( $V_{TH}$ ),  $V_{TH}$  variations must be considered to determine  $V_{BD}$ . Thus,  $V_{BD}$  is determined as  $V_{ON}$  ( $\Delta V_{TH} > 0$ ) –  $V_{OFF}$  ( $\Delta V_{TH} < 0$ ) +  $V_{MARGIN}$ , where  $V_{MARGIN}$  is added to ensure reliable discrimination.

Table I explains the impact of  $V_{BD}$  on bit discrimination, specifically for L3B discrimination. This is achieved by modulating the voltages of DATA\_LO and RF\_LO to control  $V_{GS}$  of M2 as shown in Fig. 1(a). Each L3B corresponds to a unique  $V_{DATA\_LO}$ , which defines the bit value by setting the gate voltage of M2 at  $T_{PRG}$ . As L3B increments, DATA\_LO

TABLE I

VOLTAGE LEVELS OF DATA\_LO FOR L3B DISCRIMINATION

AND RF\_LO DURING TREF

| L3B | DATA_LO                                             | $T_{REF}$ | RF_LO                                                                     |

|-----|-----------------------------------------------------|-----------|---------------------------------------------------------------------------|

| 000 | $V_{\rm DATA\_LO\_GL0}$                             | (0)       | $V_{RF\_LO(0)}$                                                           |

| 001 | $V_{DATA\_LO\_GL0} \!\!+\! 1 \!\!\times\!\! V_{BD}$ | (1)       | $V_{RF\_LO(0)}\!\!-\!1\!\times\!V_{BD}\!\!+\!\!\Delta V_{REF(1,0)}$       |

| 010 | $V_{DATA\_LO\_GL0} \!\!+\! 2 \!\!\times\! V_{BD}$   | (2)       | $V_{RF\_LO(0)}\!\!-\!\!2\!\!\times\!\!V_{BD}\!\!+\!\!\Delta V_{REF(2,0)}$ |

| 011 | $V_{DATA\_LO\_GL0} \!\!+\! 3 \!\!\times\! V_{BD}$   | (3)       | $V_{RF\_LO(0)}\!\!-\!\!3\!\times\!\!V_{BD}\!\!+\!\!\Delta V_{REF(3,0)}$   |

| 100 | $V_{DATA\_LO\_GL0}\!\!+\!\!4\!\!\times\!\!V_{BD}$   | (4)       | $V_{RF\_LO(0)}\!\!-\!\!4\!\!\times\!\!V_{BD}\!\!+\!\!\Delta V_{REF(4,0)}$ |

| 101 | $V_{DATA\_LO\_GL0} \!\!+\! 5 \!\!\times\! V_{BD}$   | (5)       | $V_{RF\_LO(0)}\!\!-\!5\!\times\!\!V_{BD}\!\!+\!\!\Delta V_{REF(5,0)}$     |

| 110 | $V_{DATA\_LO\_GL0} + 6 \times V_{BD}$               | (6)       | $V_{RF\_LO(0)}\!\!-\!\!6\!\!\times\!\!V_{BD}\!\!+\!\!\Delta V_{REF(6,0)}$ |

| 111 | $V_{DATA\_LO\_GL0} \!\!+\! 7 \!\!\times\! V_{BD}$   | (7)       | $V_{RF\_LO(0)}\!\!-\!\!7\!\!\times\!\!V_{BD}\!\!+\!\!\Delta V_{REF(7,0)}$ |

|     |                                                     | (8)       | $V_{RF\_LO(0)}\!\!+\Delta V_{REF(8,0)}$                                   |

increases by a multiple of V<sub>BD</sub> starting from V<sub>DATA LO GL0</sub>. RF\_LO modulates the gate voltage of M2 over time to enable bit discrimination across T<sub>REF</sub>. As T<sub>REF</sub> progresses, RF\_LO gradually decreases the V<sub>GS</sub> of M2 for bit discrimination, turning M2 off based on the programmed VDATA\_LO. Each RF\_LO step also must account for the change in V<sub>REF</sub> steps, which affects the V<sub>GS</sub> of M2 as a source/drain node of M2. For example, if L3B = 000, M2 should be turned on only at T<sub>REF(0)</sub> which is ensured by setting V<sub>ON</sub>+V<sub>MARGIN</sub> >  $V_{GS\_M2} = V_{DATA\_LO\_GL0} + V_{RF\_LO(0)} - V_{REF(0)} \ge V_{ON}$  at  $T_{REF(0)}$ . At  $T_{REF(1)}$ , RF\_LO is adjusted by  $V_{BD}$  for bit discrimination while also incorporating  $\Delta V_{REF(1,0)}$ , which represents the difference between REF voltages at T<sub>REF(1)</sub> and T<sub>REF(0)</sub>. At T<sub>REF(8)</sub>, RF\_LO is controlled to restore  $V_{GS\ M2}$  to its initial voltage as at  $T_{REF(0)}$ , which is given by  $V_{DATA LO GL0} + V_{RF LO(0)} - V_{REF(0)}$ .

As shown in Fig. 1(b), L3B and U3B are independently controlled through the combination of DATA\_LO with RF\_LO and DATA\_UP with RF\_UP, respectively. Bit values are defined by DATA voltages, and the corresponding RF signals modulate the gate voltage of M1 or M2 to enable bit discrimination. The initial voltages of RF\_UP (V<sub>RF\_UP(0)</sub>) and DATA\_UP (V<sub>DATA\_UP\_GL0</sub>) are chosen to initially turn on M1, while allowing bit discrimination across different U3B, similar to how V<sub>RF\_LO(0)</sub> and V<sub>DATA\_LO\_GL0</sub> are determined for M2. Although DATA\_UP and DATA\_LO operate independently and can be set independently, their voltage levels should be chosen considering the operating range of the display driver IC.

RF\_LO and RF\_UP feature 64 voltage levels during  $T_{REF}$ s, modulating the  $V_{GS}$  of M2 and M1, respectively. Thus, RF\_LO is responsible for L3B and RF\_UP is responsible for U3B. Specifically, to enable the discrimination of L3B = M at the corresponding  $T_{REF(N)}$ , RF\_LO is set to  $V_{RF_LO(0)} - \times V_{BD} + \Delta V_{REF(N,0)}$  at  $T_{REF(N)}$ , where M satisfies M = N mod 8. Similarly, RF\_UP is set to  $V_{RF_LUP(0)} - M \times V_{BD} + \Delta V_{REF(N,0)}$  at  $T_{REF(N)}$  to discriminate for U3B = M, where M satisfies M = floor(N/8).

As  $T_{REF}$  progresses, REF incrementally charges the pixel node when both M1 and M2 are on. Specifically,  $T_{REF}$  consists of 64 refresh intervals which is divided into two segments: L3B discrimination cycles (L3B disc. cycles) and U3B discrimination points (U3B disc. points), as illustrated by the left dashed box in Fig. 1(b). Each L3B disc. cycle consists of eight refresh intervals, repeated eight times throughout one  $T_{REF}$

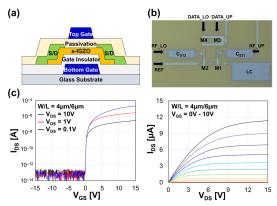

Fig. 3. (a) The cross-section view of oxide TFT [13] (b) Micrograph of the fabricated circuit (c) Transfer curve and output curve of oxide TFT  $(W/L=4\mu m/6\mu m)$ .

period, creating consistent on-off sequences based on the programmed DATA\_LO. U3B disc. points occur eight times at the start of each L3B disc. cycle, dividing the 64 refresh intervals into eight segments used to determine the U3B based on DATA UP.

For example, If the voltages of DATA\_LO and DATA\_UP are programmed to correspond 000 for the L3B and to 100 for the U3B, respectively, M1 remains on through the fifth U3B disc. point and turns off at the sixth U3B disc. point of  $T_{REF(40)}$ . M2 is activated for only one refresh interval in each L3B disc. cycle, specifically at  $T_{REF(0)}$ ,  $T_{REF(8)}$ ,  $T_{REF(16)}$ ,  $T_{REF(24)}$  and  $T_{REF(32)}$ . As a result, the pixel is charged to the voltage level corresponding to the gray level of 32 as shown in Fig. 1(b).

## C. Display Period (T<sub>DISP</sub>)

Pixel maintains the voltage determined during  $T_{REF}$  and displays the corresponding gray level during  $T_{DISP}$ . After  $T_{DISP}$ , the cycle reverts to  $T_{REF}$ , and a polarity inversion takes place, repeating the process. The proposed circuit can prevent image sticking in the LCDs through self-refresh with polarity inversion [14].

## III. RESULTS AND DISCUSSION

We fabricated the proposed circuit and verified the 6-bit depth implementation through measurement. Fig. 3 shows a micrograph of the fabricated circuit, along with a cross-sectional view of an oxide TFT, and its transfer and output curves (W/L =  $4\mu$ m/6 $\mu$ m) [13]. We employ a dual-gate structure to enhance carrier mobility and reduce the subthreshold swing [15]. The channel length of all TFTs was 6  $\mu$ m. M1 and M2 had a channel width of 4  $\mu$ m, while M3 and M4 had a width of 6  $\mu$ m.  $C_{ST1}$  and  $C_{ST2}$  were 300 fF and  $C_{LC}$  was 1 pF.

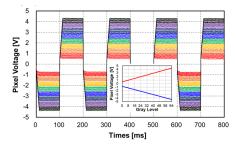

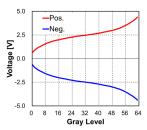

Fig. 4 illustrates the measurement results for implementation of 64 gray levels at a driving frequency of 10 Hz. The on and off levels of scan signals were 10 V and and RF\_LO during  $T_{REF}20$  V, respectively.  $T_{REF}$  was set to 200  $\mu$ s, and  $V_{BD}$  was 1.4 V, taking into account the voltage difference between  $V_{ON}$  and  $V_{OFF}$ , as well as a voltage margin to accommodate  $V_{TH}$  variations. The measured pixel voltages were ranging from  $\pm 0.6$  V to  $\pm 4.38$  V, in steps of 0.06 V.

LCDs inherently exhibit nonlinear electro-optical characteristics. By nonlinearly adjusting REF and modulating RF\_LO/RF\_UP accordingly, gamma correction can be

Fig. 4. The measurement results show that the proposed circuit can implement 64 gray levels.

Fig. 5. The simulation results incorporating LCD gamma characteristics with gamma correction.

achieved. This technique has been already reported in integrated TFT data drivers [16], [17] and in column driver ICs [18], [19]. Simulation results confirm that the proposed circuit maintains accurate and stable 6-bit grayscale operation per sub-pixel without requiring additional compensation bits, as shown in Fig. 5. In our previous study, we investigated V<sub>TH</sub> distribution and reliability using the same fabrication process [13]. For 21 oxide TFTs,  $V_{TH}$  ranged from -0.30 V to 0.06 V. Additionally, V<sub>TH</sub> shifted by 0.004 V and 0.031 V after positive bias stress (PBS) and negative bias stress (NBS) tests conducted for 10,000 seconds, respectively [13]. Reflecting the V<sub>TH</sub> distribution in V<sub>BD</sub> determination ensures stable operation as shown in Fig. 2. While a higher V<sub>BD</sub> improves tolerance to V<sub>TH</sub> variations, it also increases the signal voltage range and power consumption. Thus, V<sub>BD</sub> must be optimized considering the V<sub>TH</sub> distribution.

We calculated the power consumption of the proposed circuit under the same conditions as our previous work [13], achieving a 97.2% reduction compared to conventional 1T1C circuit. The proposed circuit also extends the sub-pixel bit depth from 3-bit to 6-bit, enabling 18-bit RGB color and increasing total colors from 512 to 262,144, increasing by 512 times. Additionally, self-refresh and gamma correction enhance grayscale accuracy while minimizing power.

#### IV. CONCLUSION

In this letter, we have proposed a 6-bit MIP circuit utilizing a novel driving scheme, effectively reducing graphics processor power consumption and preventing image sticking through self-refresh. This eliminates the need for frame memory and continuous data processing for static images. The proposed circuit achieves a substantial power reduction of 97.2 % compared to conventional circuit while it enhances grayscale representation by extending the bit depth per sub-pixel from three bits to six bits ultimately achieving an 18-bit color depth.

#### **A**CKNOWLEDGMENT

The EDA tool was supported by the IC Design Education Center (IDEC), South Korea.

#### REFERENCES

- C. R. Wiley, "DisplayPort 1.2, embedded DisplayPort, and future trends," in SID Int. Symp. Dig. Tech. Papers, vol. 42, no. 1, Aug. 2012, pp. 551–554, doi: 10.1889/1.3621384.

- [2] K. Shah, S. Kwa, and G. Hayek, "69.4: Invited paper: Extending battery life of Ultrabook through use of panel self refresh technology (PSR)," in SID Symp. Dig. Tech. Papers, Jul. 2013, vol. 44, no. 1, pp. 966–968, doi: 10.1002/j.2168-0159.2013.tb06384.x.

- [3] M.-S. Hwang, D.-J. Choe, D.-W. Kim, J.-B. Park, J.-W. Bae, W.-J. Choe, and J. O. Kwag, "16-2: Cost-effective driver IC architecture using low-power memory interface for mobile display application," in SID Symp. Dig. Tech. Papers, Jun. 2017, vol. 48, no. 1, pp. 201–203, doi: 10.1002/sdtp.11645.

- [4] H. Kimura, T. Maeda, T. Tsunashima, T. Morita, H. Murata, S. Hirota, and H. Sato, "A 2.15 inch QCIF reflective color TFT-LCD with digital memory on glass (DMOG)," in SID Int. Symp. Dig. Tech. Papers, Jun. 2001, vol. 32, no. 1, pp. 268–271, doi: 10.1889/ 1.1831847

- [5] M. Senda, Y. Tsutsui, A. Sasaki, S. Matsumoto, R. Yokoyama, and K. Yoneda, "Ultra-low-power polysilicon AMLCD with full integration," J. Soc. Inf. Display, vol. 11, no. 1, pp. 121–125, Mar. 2003, doi: 10.1889/1.1831694.

- [6] Y. Nakajima, Y. Teranishi, Y. Kida, and Y. Maki, "Ultra-low-power LTPS TFT-LCD technology using a multi-bit pixel memory circuit," J. Soc. Inf. Display, vol. 14, no. 12, p. 1071, Dec. 2006, doi: 10.1889/ 1.2408388.

- [7] K. Yamashita, K. Hashimoto, A. Iwatsu, M. Yoshiga, J. R. Ayres, M. J. Edwards, and H. Murai, "Dynamic self-refreshing memory-in-pixel circuit for low power standby mode in mobile LTPS TFT-LCD," in SID Int. Symp. Dig. Tech. Papers, May 2004, vol. 35, no. 1, pp. 1096–1099, doi: 10.1889/1.1833129.

- [8] Y. Yamauchi, N. Ueda, Y. Ogawa, K. Tanaka, and K. Yamamoto, "A novel pixel memory using integrated voltage-loss-compensation (VLC) circuit for ultra-low-power TFT-LCDs," J. Soc. Inf. Display, vol. 19, no. 1, pp. 57–62, Jan. 2011, doi: 10.1889/jsid19. 1.57.

- [9] L.-W. Chu, P.-T. Liu, and M.-D. Ker, "Design of analog pixel memory for low power application in TFT-LCDs," *J. Display Tech*nol., vol. 7, no. 2, pp. 62–69, Feb. 2011, doi: 10.1109/JDT.2010. 2089781.

- [10] S.-H. Lee, J. Kim, S. H. Yoon, K.-A. Kim, S.-M. Yoon, C. Byun, C.-S. Hwang, G. H. Kim, K.-I. Cho, and S.-W. Lee, "Pixel architecture for low-power liquid crystal display comprising oxide and ferroelectric memory thin film transistors," *IEEE Electron Device Lett.*, vol. 36, no. 6, pp. 585–587, Jun. 2015, doi: 10.1109/LED.2015.2424216.

- [11] S.-H. Lee, B.-C. Yu, H.-J. Chung, and S.-W. Lee, "Memory-in-pixel circuit for low-power liquid crystal displays comprising oxide thin-film transistors," *IEEE Electron Device Lett.*, vol. 38, no. 11, pp. 1551–1554, Nov. 2017, doi: 10.1109/LED.2017.2752803.

- [12] S. Daly and X. Feng, "Bit-depth extension: Overcoming LCD-driver limitations by using models of the equivalent input noise of the visual system," J. Soc. Inf. Display, vol. 13, no. 1, p. 51, 2005, doi: 10.1889/1.1867100.

- [13] J.-H. Jo, W.-B. Jeong, H.-J. Chung, and S.-W. Lee, "A self-refresh memory-in-pixel for low-power reflective liquid crystal displays," *IEEE Electron Device Lett.*, vol. 44, no. 1, pp. 48–51, Jan. 2023, doi: 10.1109/LED.2022.3225849.

- [14] M. Mizusaki, T. Miyashita, and T. Uchida, "Behavior of ion affecting image sticking on liquid crystal displays under application of direct current voltage," *J. Appl. Phys.*, vol. 108, no. 10, Nov. 2010, Art. no. 104903, doi: 10.1063/1.3504186.

- [15] M. Mativenga, S. An, and J. Jang, "Bulk accumulation a-IGZO TFT for high current and turn-on voltage uniformity," *IEEE Electron Device Lett.*, vol. 34, no. 12, pp. 1533–1535, Dec. 2013, doi: 10.1109/LED.2013.2284599.

- [16] S.-W. Lee, H.-J. Chung, C.-H. Lee, and C.-H. Han, "A low-power poly-Si TFT-LCD with integrated 8-bit digital data drivers," in *Proc. 18th Int. Display Res. Conf. (IDRC)*, 1998, pp. 285–288.

- [17] S.-W. Lee, H.-J. Chung, C.-H. Han, and J.-W. Lee, 'High-performance low-power integrated 8-bit digital data for poly-Si TFT-LCDs," in *Proc. SID Symp. Dig.*, vol. 30, 1999, pp. 76–79, doi: 10.1889/1.1834139.

- [18] C.-W. Lu and L.-C. Huang, "A 10-bit LCD column driver with piecewise linear Digital-to-Analog converters," *IEEE J. Solid-State Circuits*, vol. 43, no. 2, pp. 371–378, Feb. 2008, doi: 10.1109/JSSC.2007.914274.

- [19] C.-W. Lu, P.-Y. Lai Lee, Y.-G. Chang, X.-W. Huang, J.-S. Cheng, P.-Y. Tseng, C.-H. Chou, P. Chen, T.-Y. Chang, and J. Y.-C. Liu, "A 10-bit 1026-channel column driver IC with partially segmented piecewise linear digital-to-analog converters for UHD TFT-LCDs with one billion color display," *IEEE J. Solid-State Circuits*, vol. 54, no. 10, pp. 2703–2716, Oct. 2019, doi: 10.1109/JSSC.2019.2927444.